**UNIVERSIDADE FEDERAL DE PELOTAS**

**Centro de Desenvolvimento Tecnológico**

**Programa de Pós-Graduação em Computação**

**Dissertação**

**Exploração de Arquiteturas de Memórias Híbridas para Sistemas Embarcados

utilizando Memórias Não Voláteis**

**Lisandro Luiz da Silva**

Pelotas, 2017

**Lisandro Luiz da Silva**

**Exploração de Arquiteturas de Memórias Híbridas para Sistemas Embarcados

utilizando Memórias Não Voláteis**

Dissertação apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Mestre em Ciência da Computação.

Orientador: Prof. Dr. Júlio Carlos Balzano de Mattos

Coorientadora: Prof<sup>a</sup> Dr<sup>a</sup> Lisane Brisolara de Brisolara

Pelotas, 2017

Universidade Federal de Pelotas / Sistema de Bibliotecas

Catalogação na Publicação

S586e Silva, Lisandro Luiz da

Exploração de arquiteturas de memórias híbridas para sistemas embarcados utilizando memórias não voláteis / Lisandro Luiz da Silva ; Júlio Carlos Balzano de Mattos, orientador ; Lisane Brisolara de Brisolara, coorientadora. — Pelotas, 2017.

131 f.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2017.

1. Scratchpads. 2. Memórias híbridas. 3. Consumo energético. 4. Desempenho. I. Mattos, Júlio Carlos Balzano de, orient. II. Brisolara, Lisane Brisolara de, coorient. III. Título.

CDD : 005

Elaborada por Aline Herbstrith Batista CRB: 10/1737

Lisandro Luiz da Silva

Exploração de Arquiteturas de Memórias Híbridas para Sistemas Embarcados

utilizando Memórias Não Voláteis

Dissertação aprovada, como requisito parcial, para obtenção do grau de Mestre em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

Data da Defesa: 02/05/2017

Banca examinadora:

.....

Prof. Dr. Júlio Carlos Balzano de Mattos (Orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul

.....

Prof. Dr.<sup>a</sup> Lisane Brisolara de Brisolara (Coorientadora)

Doutora em Computação pela Universidade Federal do Rio Grande do Sul

.....

Prof. Dr. Mateus Beck Rutzig

Doutor em Computação pela Universidade Federal do Rio Grande do Sul

.....

Prof. Dr. Bruno Zatt

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul

.....

Prof. Dr. Felipe de Souza Marques

Doutor em Computação pela Universidade Federal do Rio Grande do Sul

**Dedico este trabalho aos meus pais e a todos

que fizeram parte e colaboraram de forma direta e

indireta na minha caminhada.**

## **Agradecimentos**

Gostaria de agradecer a todas as pessoas que me ajudaram durante esses anos de estudo. Primeiramente, agradeço aos meus pais pelo apoio incondicional em permitir que eu pudesse vencer esta etapa de minha vida, eles merecem todo o meu carinho.

Agradeço à minha namorada Itana Sena, a qual sempre esteve ao meu lado durante esses cinco anos, incentivando-me a crescer e a prosperar os desejos do meu coração. O meu muito obrigado por tudo.

Agradeço ao meu orientador professor Júlio Carlos Balzano de Mattos e a minha coorientadora professora Lisane Brisolara de Brisolara que foram fundamentais no meu crescimento acadêmico, científico e profissional. Obrigado por fazerem parte da minha caminhada, pontuando, de forma construtiva, as minhas dificuldades e motivando-me a realizar este trabalho.

Aos docentes da Universidade Federal de Pelotas, os quais tive o privilégio de ser aluno, que fizeram parte do meu processo de aprendizado, contribuindo para a minha formação. Aos meus colegas de mestrado, por terem compartilhado todo aprendizado de forma humanizada durante todo esse tempo que tivemos juntos.

Por fim, agradeço a todos os colegas e amigos pelo apoio e que contribuíram, ainda que indiretamente, para a realização deste trabalho.

*“Embora ninguém possa voltar atrás e fazer um novo

começo, qualquer um pode começar agora e fazer um novo

fim.” (CHICO XAVIER).*

## Resumo

SILVA, Lisandro L. **Exploração de Arquiteturas de Memórias Híbridas para Sistemas Embarcados utilizando Memórias Não Voláteis.** 2017. 131f. Dissertação (Mestrado em Ciência da Computação). - Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2017.

O consumo de energia é tão importante quanto o desempenho em sistemas embarcados alimentados a bateria, pois cada vez mais estes sistemas precisam processar computação intensiva com um baixo consumo energético. Devido à alta contribuição do acesso à memória no consumo total de energia de sistemas embarcados, a arquitetura de memória influencia fortemente os objetivos dos projetos dos dispositivos embarcados. Existem, na literatura, diversas técnicas de otimização do acesso à memória para sistemas embarcados, possibilitando por parte do projetista do sistema, uma exploração do espaço de projeto abrangente para a arquitetura de memória. Muitas dessas técnicas são propostas devido aos problemas enfrentados com o avanço da tecnologia, como por exemplo, a memória tradicional baseada em SRAM (*Static Random Access Memory*) *on-chip* tornou-se um gargalo em desempenho e consumo energético para o projeto de sistemas embarcados, devido ao seu alto *leakage* e latência de leitura. As tecnologias emergentes de memórias não voláteis (NVM, *Non-Volatile Memories*), tal como STT-RAM (*Spin-Transfer Torque RAM*) e PCRAM (*Phase Change RAM*), são soluções candidatas para os futuros sistemas de memória, pois elas possuem algumas vantagens sobre a memória SRAM tradicional, como por exemplo, um menor consumo energético para as operações de leitura. Este trabalho apresenta um estudo de exploração realizadas em memórias híbridas utilizando memórias não voláteis em sistemas embarcados. O trabalho apresenta a investigação do acesso à memória do processador embarcado ARMv5, a análise dos acessos realizados, juntamente com os impactos dos acessos à memória no consumo e no desempenho para diferentes modelos híbridos de memórias com tecnologias emergentes, para um determinado conjunto de benchmarks retirados do MiBench. Os resultados são significativos, pois, por exemplo, conseguiu-se aumentar o número de acessos da memória *scratchpad* (SPM) híbrida utilizando memória SRAM de 16KB, STT-RAM 32KB e PCM de 8KB (SPM 4) em cerca de 0,99% quando comparada com uma memória SPM tradicional utilizando SRAM de 32KB (SPM 1), além de reduzir em média 23,81% a latência e 49,24% o consumo energético e diminuir o *leakage* em 46,65% e a área em 16.29%.

**Palavras-chave:** Scratchpads, Memórias Híbridas, Consumo Energético, Desempenho.

## **Abstract**

SILVA, Lisandro L. **Hybrid Memory Architecture Exploration for Embedded Systems using Non-Volatile Memories.** 2017. 131f. Dissertation (Master Degree em Ciência da Computação). - Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2017.

Power consumption is as important as the performance in embedded systems battery powered, as increasingly these systems need to handle intensive computing with low power consumption. Due to the high contribution of memory access in the total power consumption of embedded systems, the memory architecture strongly influences the design objectives of the embedded devices. There are in the literature, various techniques of memory access optimization for embedded systems, allowing the system designer, a comprehensive design space exploration for the architecture of memory. Many of these techniques are proposed due to problems encountered with the advancement of technology, as for example, the traditional memory based on SRAM (Static Random Access Memory) on-chip has become a bottleneck in performance and energy consumption for the design of embedded systems, due to your high leakage and read latency. The emerging technologies of non-volatile memories (NVM, Non-Volatile Memories) as STT-RAM (Spin-Transfer Torque RAM) and PCRAM (Phase Change RAM), are candidate solutions for future memory systems because they have some advantages over traditional SRAM. This work presents explorations carried out in hybrid memories using non-volatile memories in embedded systems. First, the work displays a review of memory hierarchies, caches, scratchpads, the problems faced by embedded systems and new emerging technologies to these systems. Afterward, the work presents the investigation of memory access of the embedded processor ARMv5, the analysis of the accesses performed, along with the impacts of the memory accesses in consumption and performance for different hybrid models of memories with emerging technologies, for a given set of benchmarks taken from the MiBench. The results are significant, because, for example, we were able to increase the number of accesses of the scratchpad memory (SPM) hybrid using memory SRAM 16 KB, STT-RAM 32 KB and PCM 8 KB (SPM 4) in approximately 0.99% when compared with a traditional 32 kb SRAM using SPM (SPM 1), in addition to reducing in average 23.81% the latency and 49.24% energy consumption and decrease the leakage by 46.65% and 16.29% area.

**Keywords:** *Scratchpads, Hybrid Memories, Energy Consumption, Performance.*

## Lista de Figuras

|                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Segmentos do mercado para NVM.....                                                                     | 20 |

| Figura 2 – Vendas de chips contendo núcleos ARM.....                                                              | 21 |

| Figura 3 – Gap de desempenho existente entre Memória e Processador.....                                           | 22 |

| Figura 4 – Gap entre desempenho existente e energia.....                                                          | 27 |

| Figura 5 – Distância crescente entre as velocidades do processador e da memória.....                              | 30 |

| Figura 6 – Comportamento energético e tempo gasto em acesso a memória<br>conforme o tamanho da mesma aumenta..... | 31 |

| Figura 7 – Diferentes níveis da hierarquia de memória em computadores<br>embarcados, desktop e servidores.....    | 33 |

| Figura 8 – Exemplo de alocação de dados/instruções em uma scratchpad.....                                         | 35 |

| Figura 9 – Vista centrada em memória de um sistema computacional embarcado.                                       | 36 |

| Figura 10 – Célula STT-RAM.....                                                                                   | 38 |

| Figura 11 – Comparação da potência com o tempo para SRAM e STTMRAM durante<br>o estado ativo.....                 | 39 |

| Figura 12 – As operações set e reset da PCM.....                                                                  | 40 |

| Figura 13 – Uma matriz de células PCM e a estrutura de uma célula PCM.....                                        | 41 |

| Figura 14 – Capacidade e velocidade de acesso de diversas memórias.....                                           | 43 |

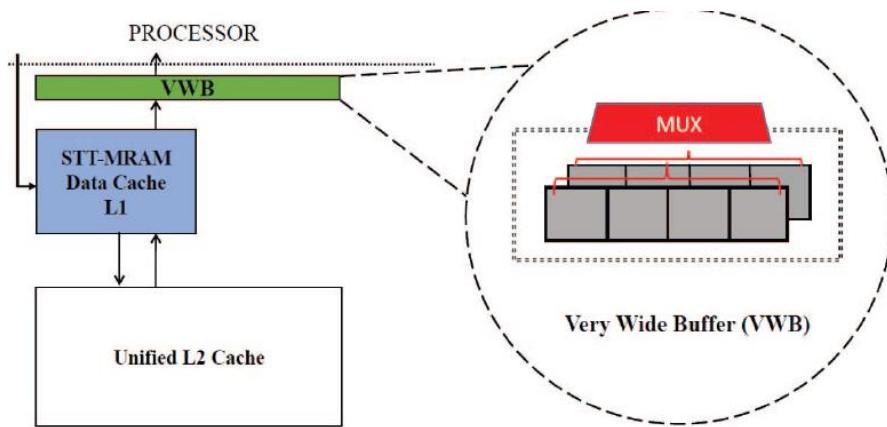

| Figura 15 – Modificação da organização D-cache L1 SRAM com uma D-cache L1<br>STT-MRAM, utilizando o VWB.....      | 50 |

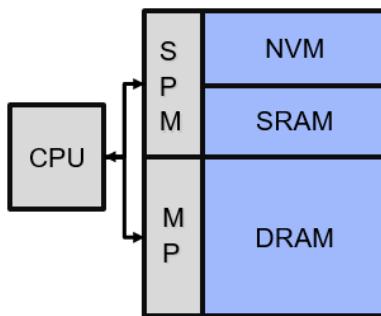

| Figura 16 – Visão geral da hierarquia de memória.....                                                             | 56 |

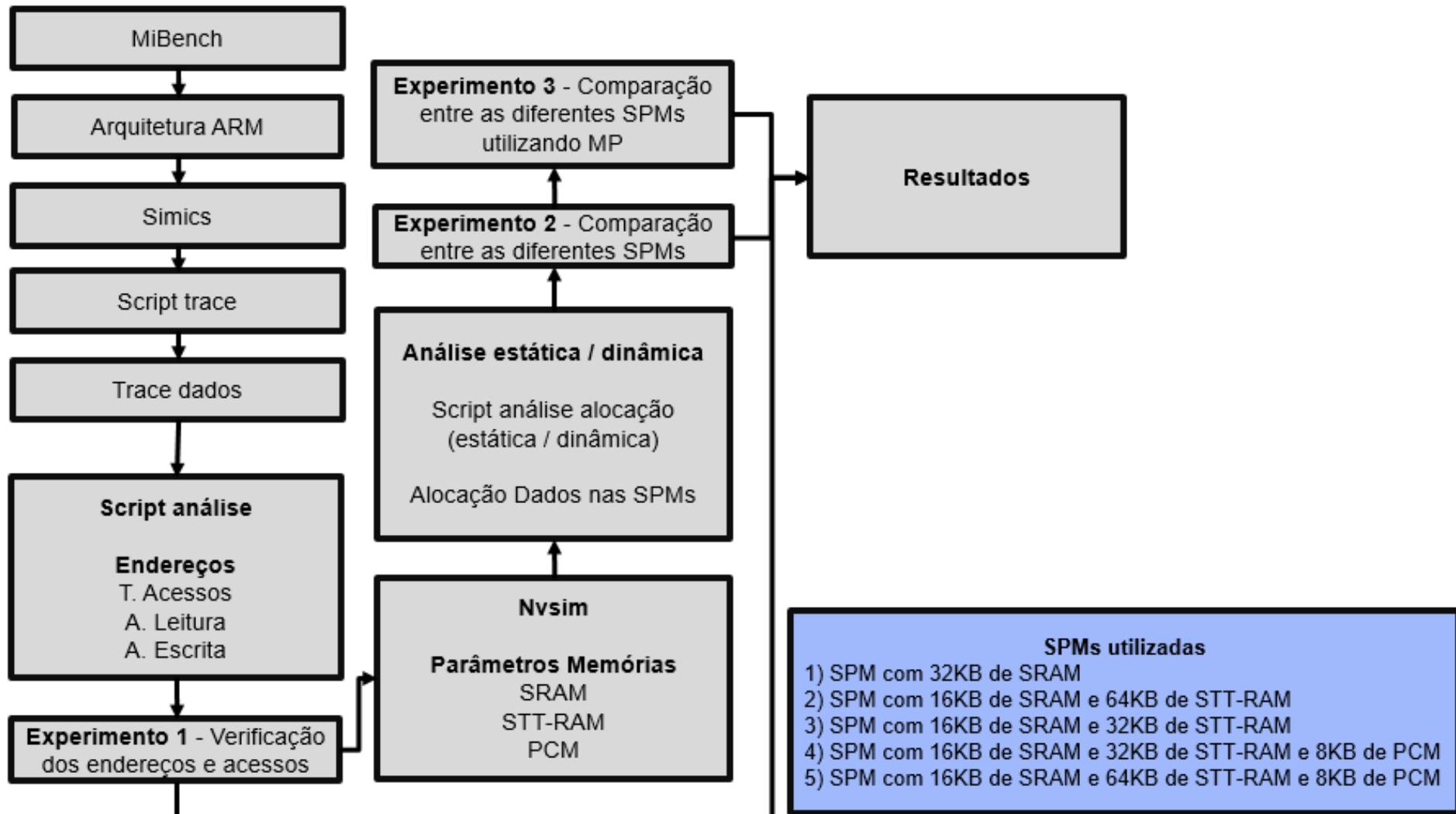

| Figura 17 – Fluxo da metodologia.....                                                                             | 59 |

| Figura 18 – Fragmento do trace de dados gerado do benchmark FFT para a<br>arquitetura ARM.....                    | 60 |

| Figura 19 – Recorte da saída do script análise para a aplicação FFT.....                                          | 61 |

| Figura 20 – Saída do script análise alocação dinâmica para a aplicação FFT.....                                   | 63 |

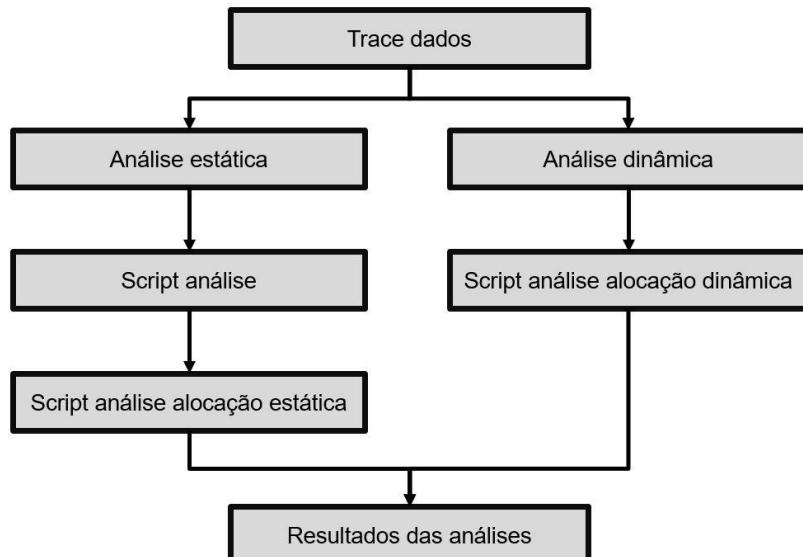

| Figura 21 – Procedimentos das análises estática e dinâmica.....                                                   | 65 |

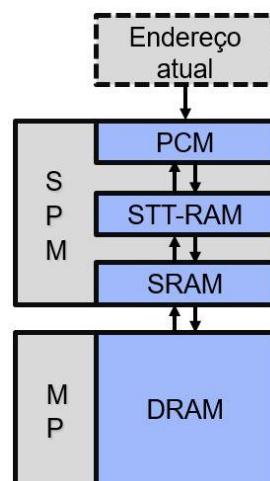

| Figura 22 – Ordem das alocações nas memórias.....                                                                 | 66 |

| Figura 23 – Recorte da saída do script análise alocação estática para a aplicação<br>FFT.....                     | 68 |

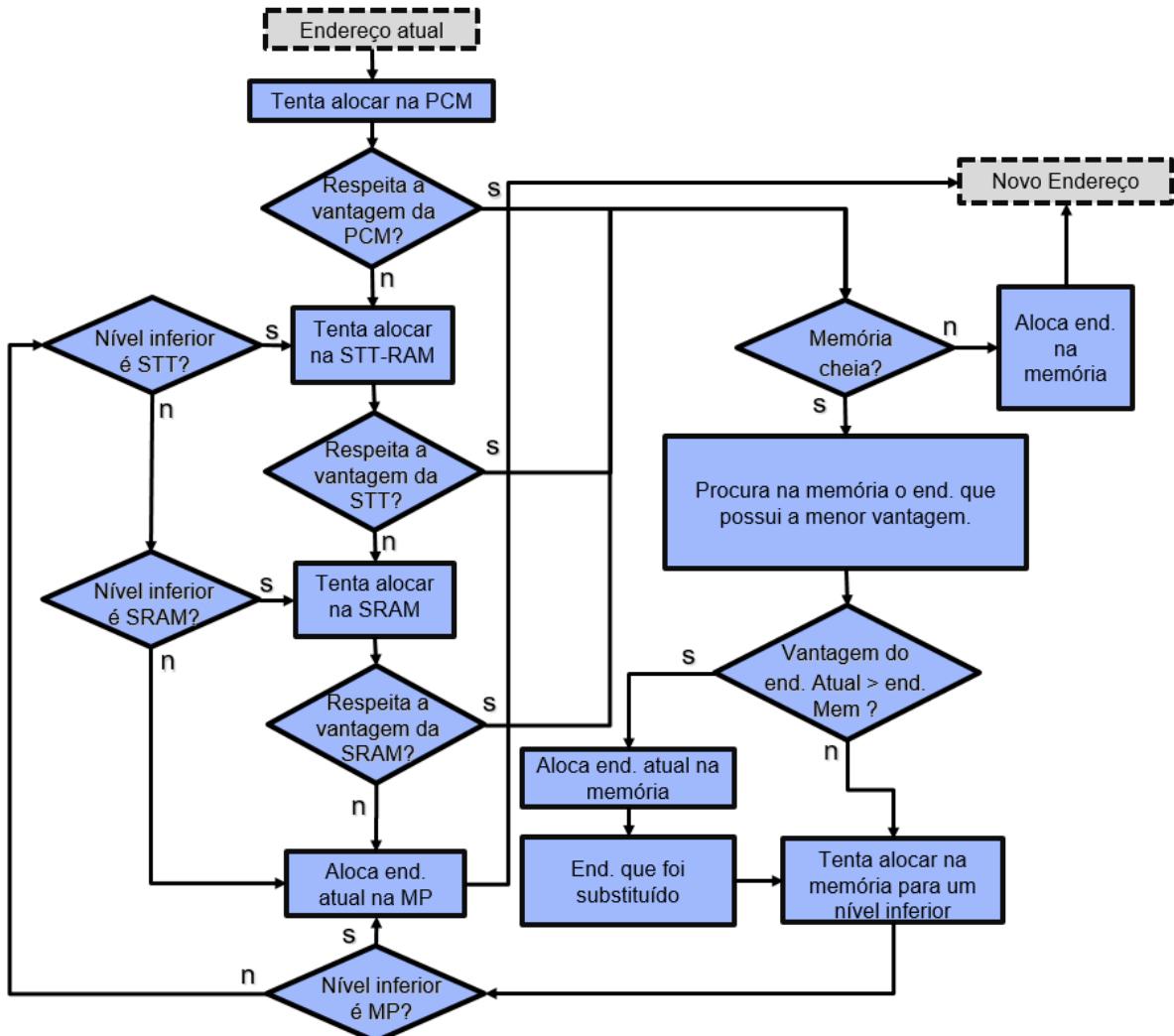

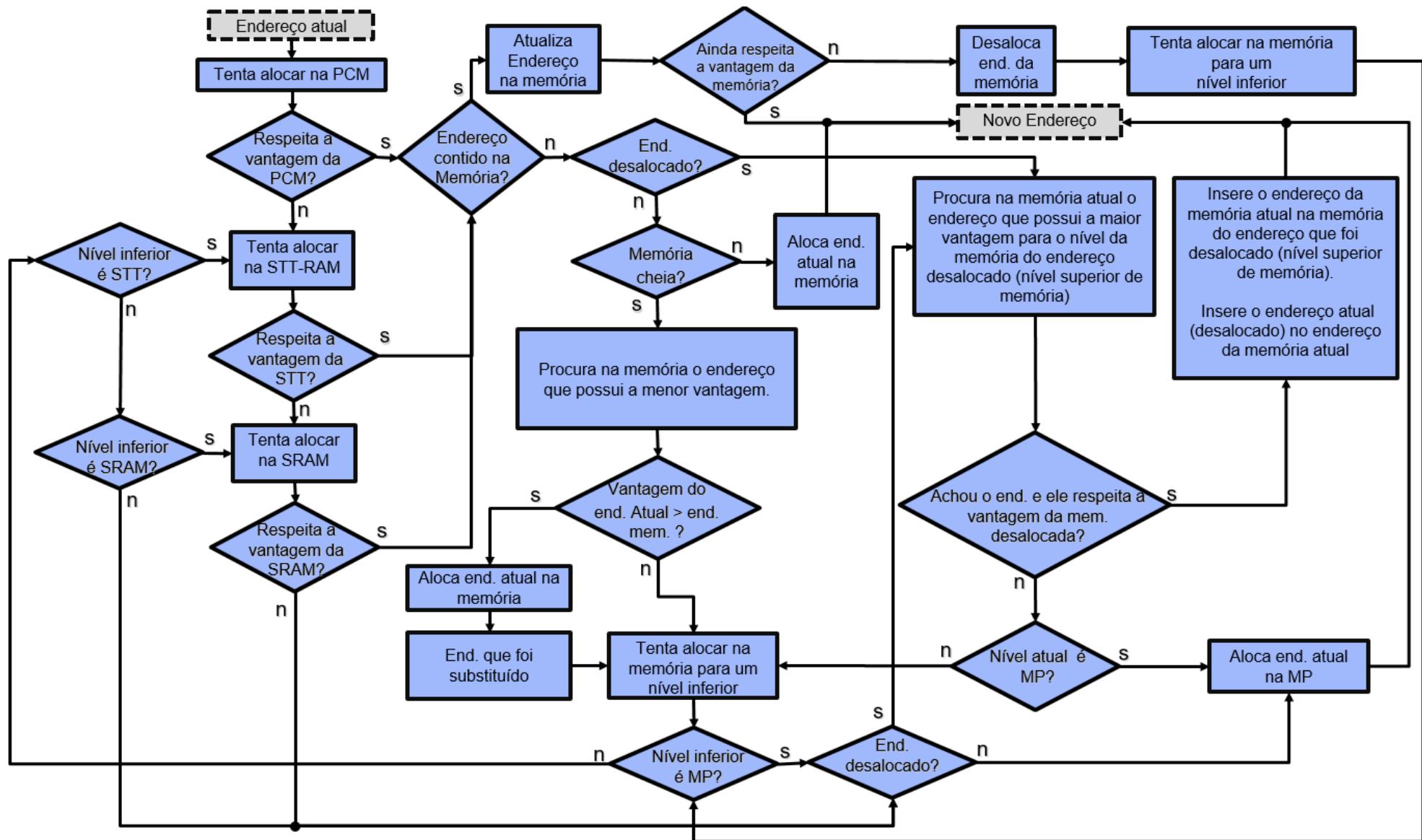

| Figura 24 – Fluxograma do script análise alocação estática.....                                                   | 70 |

|                                                                                                                                         |    |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 25 – Fluxograma do script análise alocação dinâmica.....                                                                         | 74 |

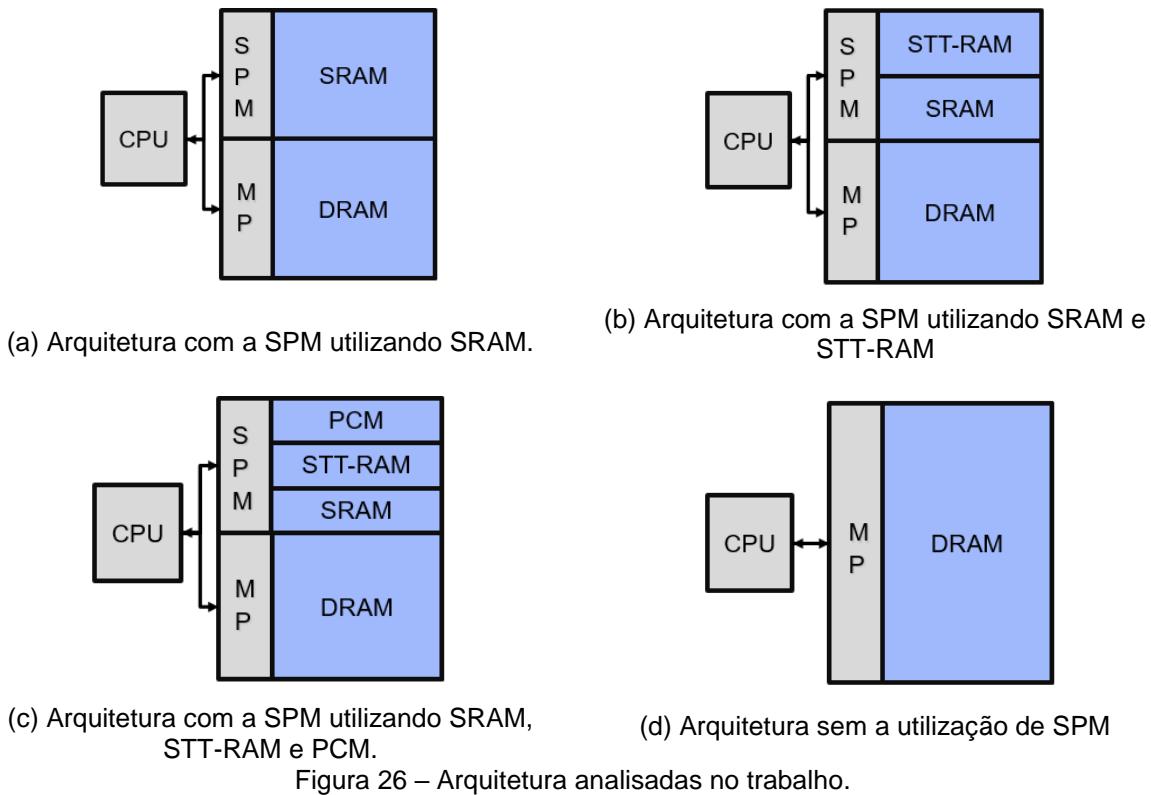

| Figura 26 – Arquitetura analisadas no trabalho.....                                                                                     | 82 |

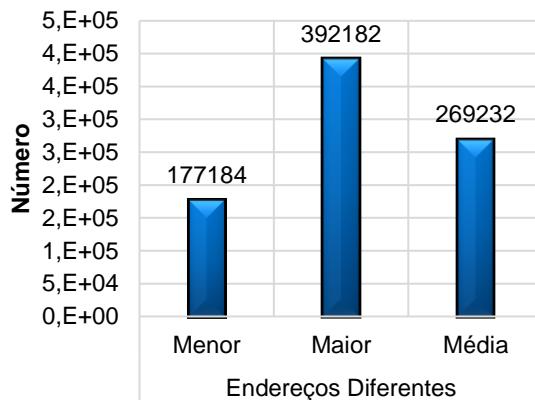

| Figura 27 – Quantidade de endereços diferentes para todas as aplicações.....                                                            | 84 |

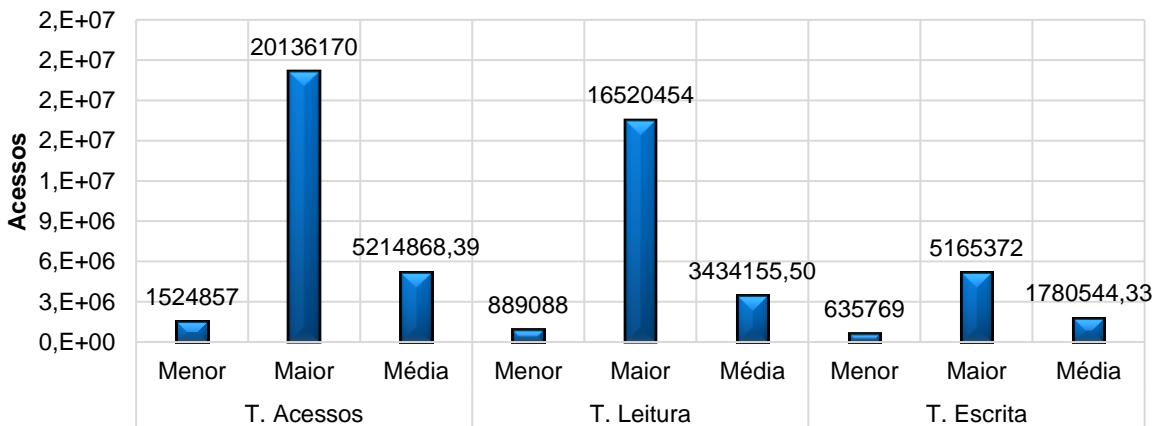

| Figura 28 – Total de acessos, total das operações de escritas e leituras. ....                                                          | 84 |

| Figura 29 – Comparação de memórias utilizando os endereços que possuem uma maior frequência de acessos. ....                            | 86 |

| Figura 30 – Comparação dos endereços com maior frequência de acessos para a operação de leitura e escrita.....                          | 87 |

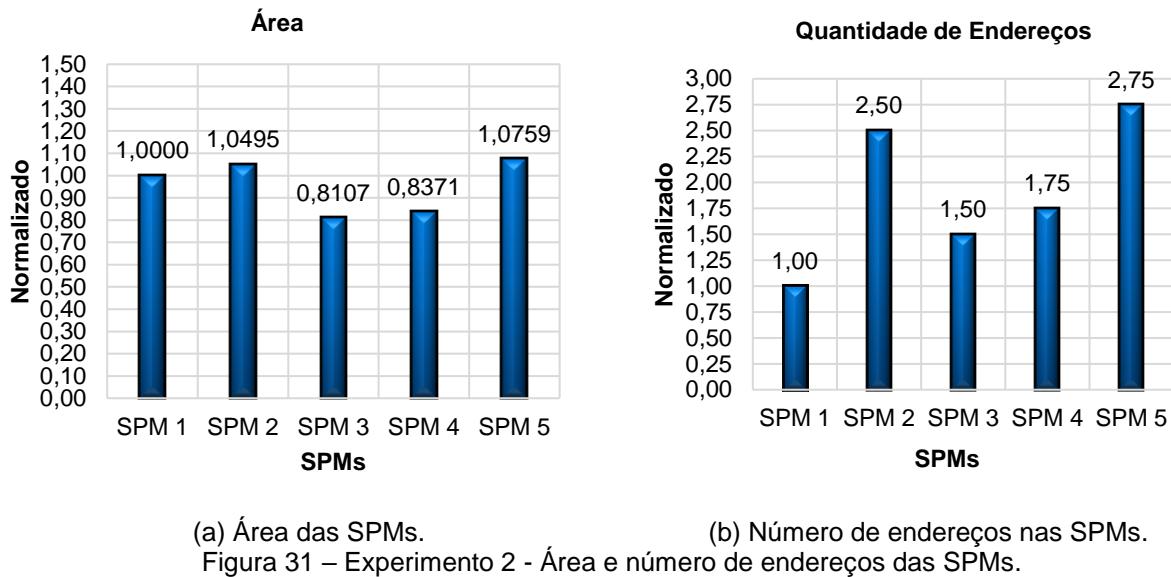

| Figura 31 – Experimento 2 - Área e número de endereços das SPMs. ....                                                                   | 89 |

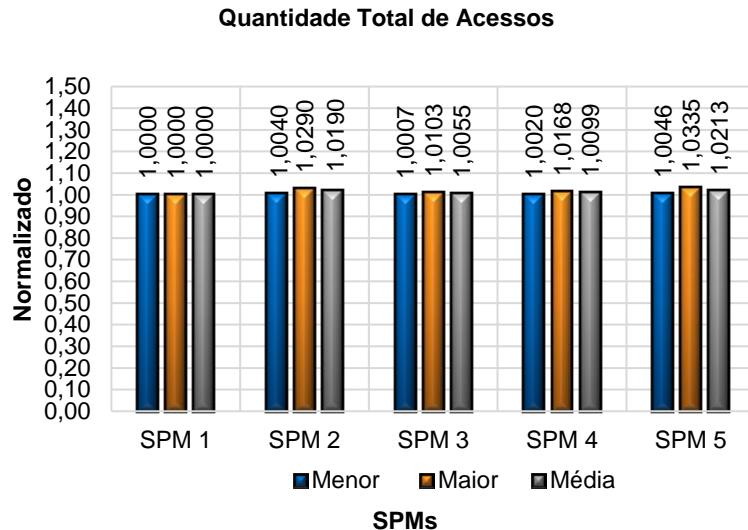

| Figura 32 – Experimento 2 - Número total de acessos nas SPMs. ....                                                                      | 90 |

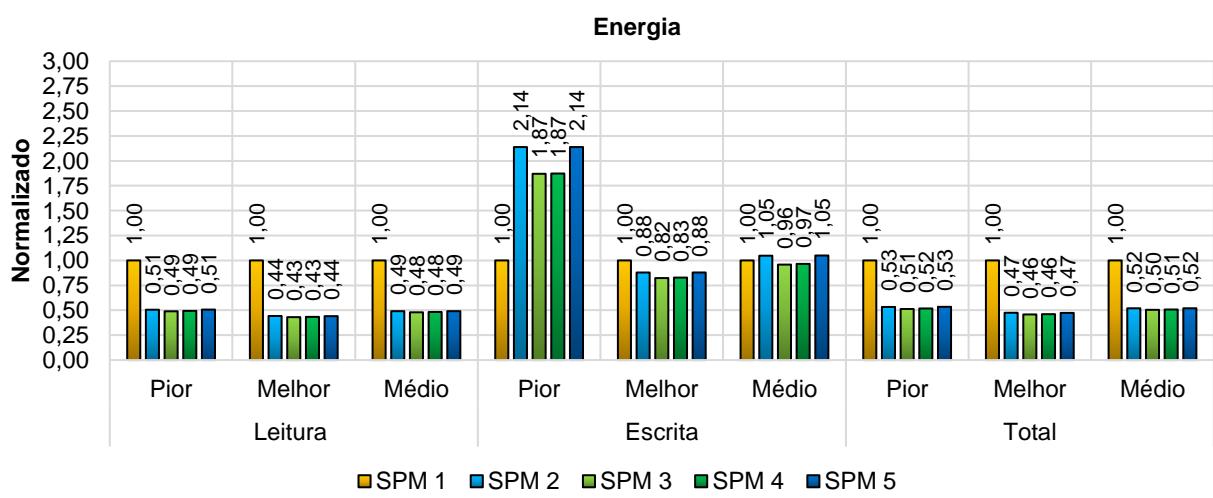

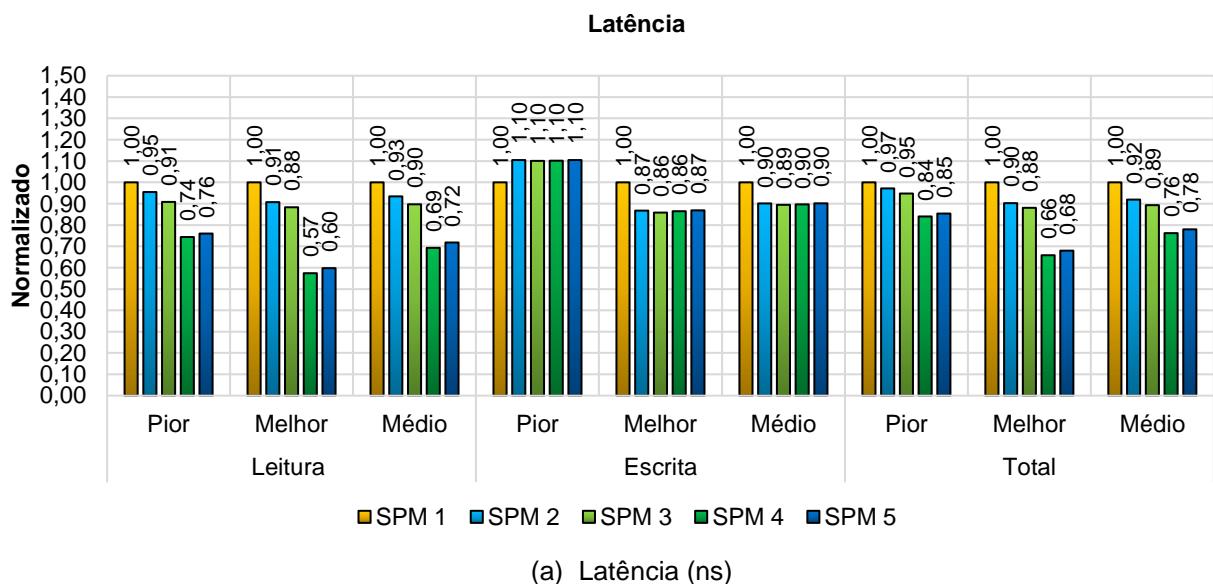

| Figura 33 – Experimento 2 - Latência e energia para as SPMs. ....                                                                       | 91 |

| Figura 34 – Experimento 2 – Produto da energia, do delay e da área para as SPMs.                                                        |    |

| .....                                                                                                                                   | 92 |

| Figura 35 – Experimento 2 - Leakage para as SPMs.....                                                                                   | 93 |

| Figura 36 – Experimento 3 - Área total da arquitetura da figura 26 (d), após as inserções das SPMs. ....                                | 94 |

| Figura 37 – Experimento 3 - Latência e energia para a arquitetura da figura 26 (d), após as inserções das SPMs.....                     | 95 |

| Figura 38 – Experimento 2 - Produto da energia, do delay e da área para a arquitetura da figura 26 (d), após as inserções das SPMs..... | 96 |

| Figura 39 – Experimento 3 - Leakage da arquitetura da figura 26 (d) após as inserções das SPMs. ....                                    | 97 |

| Figura 40 – Comparação das análises estática e dinâmica, para o experimento 2...98                                                      |    |

| Figura 41 – Comparação das análises estática e dinâmica, para o experimento 3...99                                                      |    |

## Lista de Tabelas

|                                                                                                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| Tabela 1 – Características das diferentes tecnologias de memórias .....                            | 44  |

| Tabela 2 – Propriedades aproximadas em nível do dispositivo das tecnologias de memórias .....      | 44  |

| Tabela 3 – Configurações das scratchpads .....                                                     | 57  |

| Tabela 4 – Parâmetros para a NVM e SRAM.....                                                       | 62  |

| Tabela 5 – Parâmetros para a DRAM .....                                                            | 63  |

| Tabela 6 – Fórmulas para os cálculos das latências e energias .....                                | 64  |

| Tabela 7 – Significados dos campos para o script análise .....                                     | 67  |

| Tabela 8 – Significados dos campos para o script análise alocação estática .....                   | 68  |

| Tabela 9 – Significados dos campos para o script análise alocação dinâmica .....                   | 71  |

| Tabela 10 – Classificação dos benchmarks do MiBench dentro de suas correspondentes categorias..... | 76  |

| Tabela 11 – Memórias de 4 bytes até 2 Kbytes para os traces entre os números 1 e 5.....            | 110 |

| Tabela 12 – Memórias de 4 Kbytes até 2 Mbytes para os traces entre os números 1 e 5.....           | 111 |

| Tabela 13 – Memória de 4 Mbytes e informações dos traces entre os números 1 e 5 .....              | 112 |

| Tabela 14 – Memórias de 4 bytes até 2 Kbytes para os traces entre os números 6 e 10.....           | 113 |

| Tabela 15 – Memórias de 4 Kbytes até 2 Mbytes para os traces entre os números 6 e 10.....          | 114 |

| Tabela 16 – Memória de 4 Mbytes e informações dos traces entre os números 6 e 10 .....             | 115 |

| Tabela 17 – Memórias de 4 bytes até 2 Kbytes para os traces entre os números 11 e 15.....          | 116 |

| Tabela 18 – Memórias de 4 Kbytes até 2 Mbytes para os traces entre os números 11 e 15.....         | 117 |

| Tabela 19 – Memória de 4 Mbytes e informações dos traces entre os números 11 e 15.....             | 118 |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| Tabela 20 – Memórias de 4 bytes até 2 Kbytes para os traces entre os números 16 e 18.....    | 119 |

| Tabela 21 – Memórias de 4 Kbytes até 2 Mbytes para os traces entre os números 16 e 18.....   | 120 |

| Tabela 22 – Memória de 4 Mbytes e informações dos traces entre os números 16 e 18.....       | 121 |

| Tabela 23 – Memórias de 4 bytes até 4 Kbytes para todos os traces .....                      | 122 |

| Tabela 24 – Memórias de 8 Kbytes até 4 Mbytes para todos os traces .....                     | 123 |

| Tabela 25 – Comparação entre as SPMs para a análise estática parte 1 (linha base SPM 1)..... | 124 |

| Tabela 26 – Comparação entre as SPMs para a análise estática parte 2 (linha base SPM 1)..... | 125 |

| Tabela 27 – Comparação entre as SPMs para a análise dinâmica parte 1 (linha base SPM 1)..... | 126 |

| Tabela 28 – Comparação entre as SPMs para a análise dinâmica parte 2 (linha base SPM 1)..... | 127 |

| Tabela 29 – Comparação entre as SPMs para a análise estática parte 1 (linha base DRAM) ..... | 128 |

| Tabela 30 – Comparação entre as SPMs para a análise estática parte 2 (linha base DRAM) ..... | 129 |

| Tabela 31 – Comparação entre as SPMs para a análise dinâmica parte 1 (linha base DRAM) ..... | 130 |

| Tabela 32 – Comparação entre as SPMs para a análise dinâmica parte 2 (linha base DRAM) ..... | 131 |

## **LISTA DE ABREVIATURAS E SIGLAS**

|            |                                                                  |

|------------|------------------------------------------------------------------|

| ABS        | Anti-Lock Braking System                                         |

| CPU        | Central Processing Unit                                          |

| DRAM       | Dynamic Random-Access Memory                                     |

| DVD        | Digital Versatile Disc                                           |

| DWM        | Domain Wall Memory                                               |

| EDP        | Product Energy- <i>Delay</i>                                     |

| eDRAM      | Embedded Dynamic Random-Access Memory                            |

| FBDRAM     | Floating Body Dynamic Random-Access Memory                       |

| FRAM/FeRAM | Ferro-magnetic Random-Access Memory                              |

| GPS        | Global Positioning System                                        |

| HMC        | Híbrido Memória Cubo                                             |

| IPC        | Instruções Por Ciclo                                             |

| MLC        | Multi-Level Cell                                                 |

| MP         | Memória Principal                                                |

| MRAM       | Magnetoresistive Random-Access Memory                            |

| MTJ        | Magnetic tunnel junction                                         |

| NVM        | Non-Volatile Memories                                            |

| PCM        | Phase Change Memory                                              |

| PCRAM      | Phase Change Random-Access Memory                                |

| PMTJ       | Perpendicular Magnetic Tunnel Junction                           |

| p-STT-MRAM | Perpendicular Spin-Transfer Torque Magnetic Random-Access Memory |

| RAM        | Random-Access Memory                                             |

| RDRAM      | Rambus Dynamic Random-Access Memory                              |

| RISC       | Reduced Instruction Set Computer                                 |

| RRAM/ReRAM | Resistive Random-Access Memory                                   |

| SDRAM      | Synchronous Dynamic Random-Access Memory                         |

| SLC        | Single-Level Cell                                                |

|          |                                                    |

|----------|----------------------------------------------------|

| SMC      | Smart Memory Cube                                  |

| SoC's    | System-On-Chip                                     |

| SPM      | Scratchpad Memory                                  |

| SRAM     | Static Random-Access Memory                        |

| SSD      | Solid-State Drive                                  |

| STT-MRAM | Spin-Transfer Torque Magnetic Random-Access Memory |

| STT-RAM  | Spin-Transfer Torque Random-Access Memory          |

| VLIW     | Very Long Instruction Word                         |

| VM       | Volatile Memories                                  |

| VWB      | Very Wide Buffer                                   |

## SUMÁRIO

|                                                                                    |           |

|------------------------------------------------------------------------------------|-----------|

| <b>1 INTRODUÇÃO .....</b>                                                          | <b>18</b> |

| <b>1.1 Motivação .....</b>                                                         | <b>21</b> |

| <b>1.2 Objetivos .....</b>                                                         | <b>23</b> |

| <b>1.3 Organização do Trabalho .....</b>                                           | <b>23</b> |

| <b>2 FUNDAMENTAÇÃO .....</b>                                                       | <b>25</b> |

| <b>2.1 Sistemas Embarcados.....</b>                                                | <b>25</b> |

| <b>2.2 Sistemas de Memória .....</b>                                               | <b>29</b> |

| <b>2.2.1 Hierarquia de Memória.....</b>                                            | <b>31</b> |

| <b>2.2.2 Caches.....</b>                                                           | <b>34</b> |

| <b>2.2.3 Scratchpads .....</b>                                                     | <b>34</b> |

| <b>2.3 Tecnologias Emergentes em Memórias.....</b>                                 | <b>36</b> |

| <b>2.3.1 Embedded DRAM .....</b>                                                   | <b>37</b> |

| <b>2.3.2 STT-RAM .....</b>                                                         | <b>37</b> |

| <b>2.3.3 RRAM.....</b>                                                             | <b>39</b> |

| <b>2.3.4 PCM .....</b>                                                             | <b>40</b> |

| <b>2.3.5 DWM .....</b>                                                             | <b>41</b> |

| <b>2.3.6 Comparativo entre as Tecnologias Emergentes .....</b>                     | <b>42</b> |

| <b>3 TRABALHOS RELACIONADOS .....</b>                                              | <b>45</b> |

| <b>3.1 Otimizações realizadas em Caches.....</b>                                   | <b>48</b> |

| <b>3.2 Otimizações realizadas em Scratchpads .....</b>                             | <b>51</b> |

| <b>4 AVALIAÇÃO DE HIERARQUIA DE MEMÓRIA UTILIZANDO MEMÓRIAS NÃO VOLÁTEIS .....</b> | <b>55</b> |

| <b>4.1 Hierarquia de Memória Proposta.....</b>                                     | <b>55</b> |

| <b>4.2 Metodologia.....</b>                                                        | <b>56</b> |

| <b>4.2.1 Análise Estática e Dinâmica .....</b>                                     | <b>64</b> |

| <b>4.2.1.1 Análise Estática .....</b>                                              | <b>66</b> |

| <b>4.2.1.2 Análise Dinâmica .....</b>                                              | <b>70</b> |

| <b>4.2.1.3 Diferença entre a Análise Estática e Dinâmica.....</b>                  | <b>75</b> |

| <b>4.2.2 Benchmarks Analisados.....</b>                                            | <b>75</b> |

| <b>4.2.3 Arquitetura Analisada .....</b>                                           | <b>76</b> |

| <b>4.2.4 Ferramentas de Simulação e Estimativa .....</b>                           | <b>77</b> |

| <b>4.2.4.1 Simics .....</b>                                                        | <b>78</b> |

| <b>4.2.4.2 Ferramenta NVSim.....</b>                                               | <b>79</b> |

| <b>4.2.4.3 Ferramenta Cacti.....</b>                                               | <b>80</b> |

| <b>4.2.5 Experimentos realizados .....</b>                                         | <b>81</b> |

| <b>4.2.5.1 Experimento 1 - Acessos .....</b>                                       | <b>81</b> |

| <b>4.2.5.2 Experimento 2 e 3 - Exploração de diferentes SPMs .....</b>             | <b>81</b> |

| <b>5 RESULTADOS EXPERIMENTAIS .....</b>                                            | <b>83</b> |

| <b>5.1 Experimento 1 - Verificação dos endereços e acessos.....</b>                | <b>83</b> |

| <b>5.2 Experimentos 2 e 3 - Comparaçao entre as diferentes SPMs .....</b>          | <b>87</b> |

| <b>5.2.1 Experimento 2 - Comparaçao entre as diferentes SPMs .....</b>             | <b>88</b> |

|                                                                                    |            |

|------------------------------------------------------------------------------------|------------|

| <b>5.2.2 Experimento 3 - Comparação entre as diferentes SPMs utilizando MP ...</b> | <b>93</b>  |

| <b>5.3 Comparação entre os resultados da Análise Dinâmica e Estática.....</b>      | <b>97</b>  |

| <b>6 CONCLUSÕES E TRABALHOS FUTUROS .....</b>                                      | <b>100</b> |

| <b>REFERÊNCIAS.....</b>                                                            | <b>103</b> |

| <b>APÊNDICES .....</b>                                                             | <b>109</b> |

## 1 INTRODUÇÃO

Nas últimas décadas, o crescimento da tecnologia tem se mostrado abrangente em diversas áreas, como, telecomunicações, eletrônica de consumo, meios de transporte, equipamentos médicos, entretenimento, entre outras. Esse crescimento tecnológico trouxe consigo o uso de sistemas computacionais, os quais são responsáveis por facilitar o cotidiano das pessoas. Os sistemas computacionais podem ser encontrados em diversas aplicações, como exemplificação tem-se o avanço dos aparelhos celulares, os quais acabam se tornando cada vez mais complexos, possuindo diversas funcionalidades se comparados com aparelhos celulares de poucos anos atrás. Houve um aumento significativo da convergência de diversas funcionalidades em um único aparelho. Os primeiros aparelhos telefônicos móveis tinham a função de somente realizarem ligações, com o passar do tempo, os mesmos foram ganhando mais funcionalidades, como por exemplo, a inserção de câmera digital, MP3 player, e principalmente o acesso à internet. Os sistemas computacionais quando utilizados em sistemas ainda mais complexos, são chamados de sistemas embarcados (MARWEDEL, 2011).

A diferença entre um computador de uso geral para um sistema embarcado é que, um computador de uso geral é concebido para ser flexível e executar uma vasta gama de aplicações diferentes, enquanto que sistemas embarcados são utilizados para controlar uma determinada aplicação (GAJSKI, et al. 2009). Um sistema embarcado realiza um conjunto de tarefas predefinidas, geralmente com requisitos específicos, pois o sistema é dedicado a tarefas específicas. Também são projetados para executar funções dedicadas muitas vezes com restrições de computação em tempo real. Atualmente, as aplicações desses sistemas tornam-se cada vez mais complexas, mesmo com o aumento da capacidade de processamento dos sistemas digitais modernos, contudo, o tempo para comercialização (*time-to-market*) torna-se cada vez menor.

Os sistemas embarcados possuem características que os diferem dos demais sistemas, como por exemplo, confiabilidade, custo, restrições de tempo real, tamanho do código, desempenho, baixo consumo energético, limitações físicas

(tamanho e peso), devem ser consideradas no desenvolvimento destes sistemas. Dentre os desafios encontrados no projeto destes sistemas, destaca-se a preocupação com o consumo energético e desempenho. Estes requisitos têm motivado a investigação de técnicas de otimização que diminuem o consumo energético sem que ocorra uma degradação do desempenho original, ou que aumente o desempenho sem que ocorra um grande aumento do consumo energético do sistema. A hierarquia de memória influência fortemente o desempenho e consumo energético, pois, de acordo com a hierarquia empregada, o tempo e o consumo energético do acesso ao endereço possuirá resultados diferentes dependendo do nível da hierarquia, do tipo e do tamanho da memória empregada que o endereço está contido.

Muitas dessas técnicas utilizam memórias não voláteis (NVM, *Non-Volatile Memories*) como uma forma de otimização, visto que essas memórias emergentes possuem algumas vantagens em relação as memórias tradicionais DRAM (*Dynamic Random-Access Memory*) e SRAM (*Static Random-Access Memory*), como observado nos trabalhos de Wang et al. (2012), Li et al. (2012) e Hu et al. (2013), onde estes trabalhos admitem que a memória principal NVM pode alcançar uma economia energética expressiva com o desempenho comparável ao de uma memória principal tradicional DRAM. Como alguns exemplos de memórias emergentes podemos citar a PCM (*Phase Change Memory*) ou PCRAM (*Phase Change Random-Access Memory*), a MRAM (*Magnetoresistive Random-Access Memory*), a STT-MRAM (*Spin-Transfer Torque Magnetic Random-Access Memory*) também chamada de STT-RAM (*Spin-Transfer Torque Random-Access Memory*), a RRAM/ReRAM (*Resistive Random-Access Memory*), a FRAM/FeRAM (*Ferromagnetic Random-Access Memory*) e a DWM (*Domain Wall Memory*).

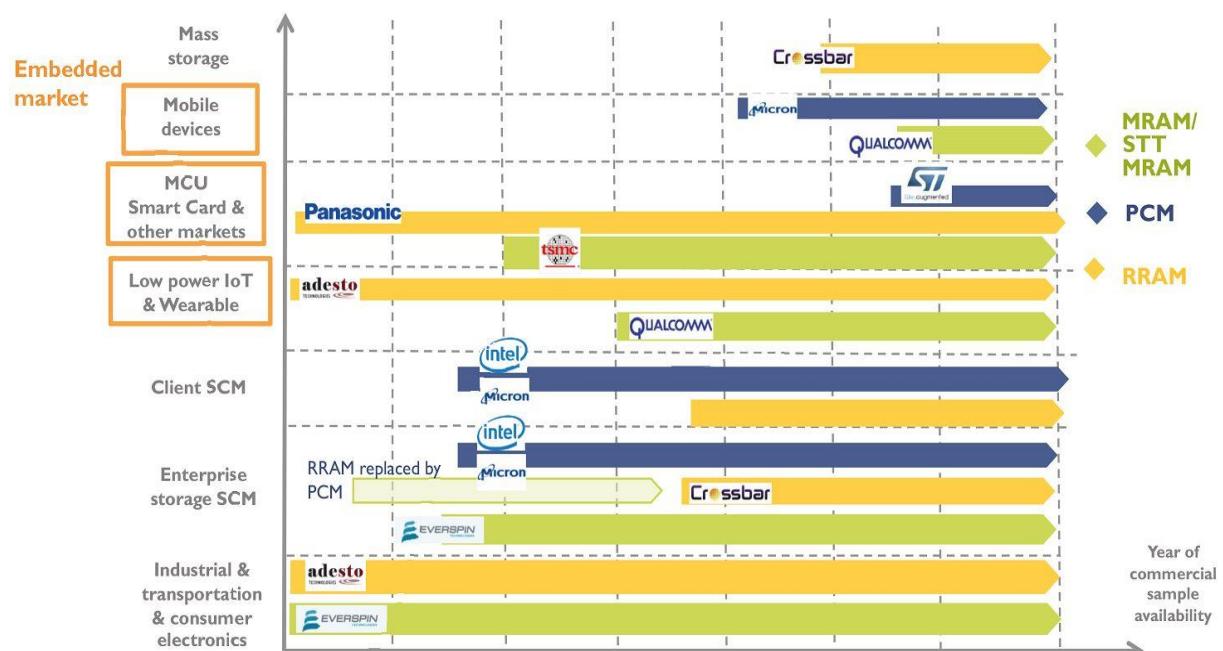

As vendas de NVM ainda são moderadas, segundo a empresa de consultoria Développement (2016), o mercado emergente de NVM em 2015 é consideravelmente mais baixo do que os negócios voláteis dominantes da DRAM e da memória *flash* não-volátil, que possuem receitas combinadas de quase 80 bilhões de dólares, enquanto que as vendas de NVMs representam cerca de 53 milhões de dólares em 2015. Entretanto, a mesma empresa prevê que o mercado NVM emergente mundial subirá de 53 milhões de dólares em 2015, para 4.6 bilhões dólares até 2021. Apresentando assim, um impressionante crescimento maior que 110% ao ano. Sob esta nova análise, a empresa de consultoria descreve como as

tecnologias NVM emergentes serão cada vez mais utilizadas em vários mercados. Os principais segmentos do mercado que foram identificados pelos analistas da empresa são apresentados na Figura 1, juntamente com o tipo de NVM utilizada e as empresas investidoras.

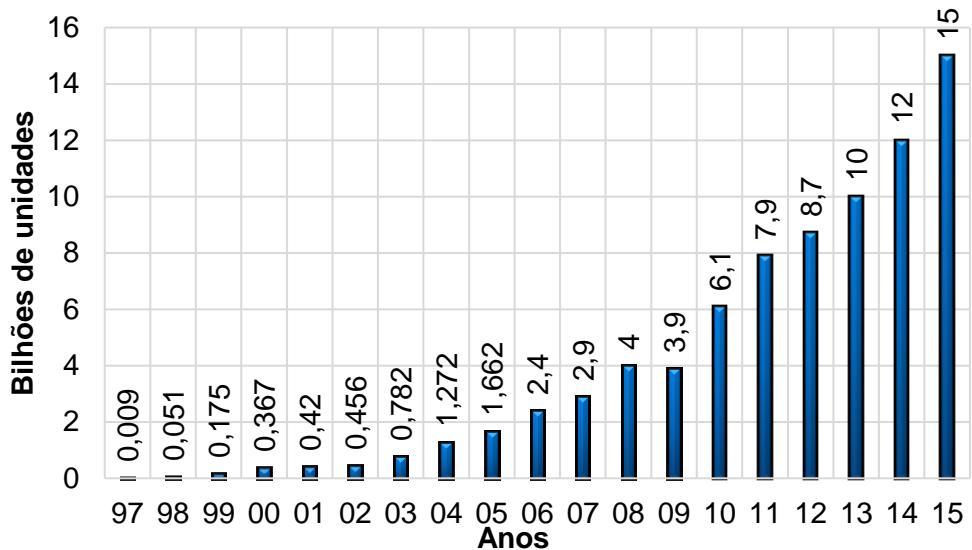

Diversos sistemas embarcados possuem em seu interior um processador ARM. Esse processador tinha mais de 95% de participação no mercado de smartphones, 10% em computadores móveis, 35% em TVs digitais em 2010 (MORGAN, 2011). A partir do ano de 2014, a empresa ultrapassou a marca dos 50 bilhões de chips produzidos, 10 bilhões foram produzidos somente em 2013 (SHIMPI, 2014). Na Figura 2 é observado o número de unidades vendidas de chips contendo núcleos ARM entre os anos de 1997 e 2015. Assim, a arquitetura que será analisada neste trabalho é a arquitetura ARM, devido ao fato da sua grande utilização em sistemas embarcados.

Figura 1 – Segmentos do mercado para NVM.

Fonte: DÉVELOPPEMENT, 2016.

Figura 2 – Vendas de chips contendo núcleos ARM

Fonte: Adaptado de ARM (2017), HEXUS (2015) e BEDDARD (2016).

## 1.1 Motivação

Os sistemas embarcados caracterizam-se por apresentar muitas restrições e requisitos, como citado anteriormente. De um modo geral a descrição dos requisitos funcionais não é suficiente para o projeto de um sistema embarcado, devendo ser considerados também requisitos não-funcionais, tais como desempenho, custo, consumo de energia, tamanho físico e peso (WOLF, 2012). Estas e outras características têm um forte impacto no projeto destes sistemas, tanto no projeto do *hardware* como no projeto do *software*.

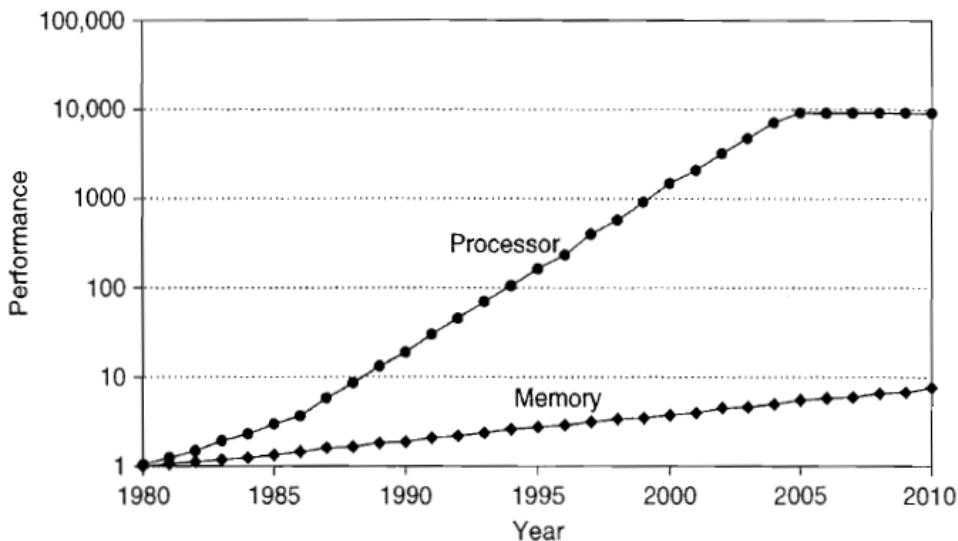

Segundo Hennessy e Patterson (2011), em um sistema de computador moderno o gargalo dominante na obtenção de alto desempenho e eficiência energética é a distância tecnológica entre o desempenho do processador e da memória tradicional, como demonstrado na Figura 3. Esta distância torna-se mais significativa em sistemas embarcados. Segundo Wolf e Kandemir (2003), o sistema de memória é um dos principais fatores de desempenho e consumo energético, especialmente nos sistemas embarcados que utilizam bateria. Como dito anteriormente, o projeto de sistemas embarcados apresenta muitas restrições e requisitos rígidos. Sendo assim, os projetistas possuem limitações em suas decisões, por causa desses requisitos não-funcionais extras, essas decisões não podem considerar apenas o desempenho, mas também o consumo energético dos dispositivos embarcados.

Figura 3 – Gap de desempenho existente entre Memória e Processador.

Fonte: HENNESSY e PATTERSON, 2011.

Com a alta contribuição da energia gasta para o acesso à memória no consumo total da mesma em sistemas embarcados, a arquitetura de memória possui uma forte influência sobre os objetivos do projeto em sistema embarcados. As memórias *caches* são normalmente utilizadas para melhorar o desempenho. Entretanto, o desempenho total do sistema e o consumo de energia são severamente relacionados com o tempo de acesso à memória e o consumo de energia média, o que faz com que a arquitetura de uma memória *cache* seja uma grande preocupação em projetos de processadores embarcados. Portanto, o projetista do sistema precisa realizar uma exploração do espaço de projeto abrangente para a arquitetura de memória.

Na literatura foram propostos vários tipos de otimizações em memória, como técnicas orientadas a loop, procedimento de *inlining* e o desenrolamento de laços (*loop unrolling*), como por exemplo no trabalho de Wolf e Kandemir (2003), as quais são exemplos de otimizações em *software*. Geralmente as abordagens tradicionais são otimizações de *hardware* ou de *software*, mas existem técnicas mistas que são relacionadas tanto ao *hardware* como ao *software*.

Visando explorar diferentes tecnologias, nos últimos anos diversos trabalhos estão utilizando NVMs com o intuito de melhorar os resultados das tradicionais DRAM e SRAM. Esses trabalhos mostram vantagens na utilização de memórias não voláteis em sistemas embarcados. Podemos citar os trabalhos de Wang et al. (2012 e 2013), Li et al. (2012), Hu et al. (2013) e Komalan et al. (2015), que utilizam algum tipo de NVM em seu desenvolvimento. O presente trabalho tem por motivação os

trabalhos de Wang et al. (2013) e Hu et al. (2013), em que os autores conseguiram diminuir o consumo energético e melhorar o desempenho através da comparação de abordagens híbridas de memórias com modelos tradicionais de memórias SRAMs, ambos os trabalhos utilizaram uma SPM (*Scratchpad Memory*) como um estudo de caso e apenas um tipo de memória emergente.

Sendo assim, o presente trabalho justifica-se pela necessidade de reduzir o consumo energético e aumentar o desempenho dos sistemas embarcados que utilizam a arquitetura ARM, através da utilização das novas tecnologias que estão surgindo no mercado de sistemas embarcados, as chamadas memórias emergentes, sendo de grande relevância para uma melhor eficiência energética e processamento desses sistemas.

## 1.2 Objetivos

Este trabalho tem como objetivo a exploração de arquiteturas de memórias híbridas para sistemas embarcados. Através dessa exploração busca-se, investigar o consumo energético e o desempenho nos acessos à memória para uma arquitetura ARM, explorando aspectos de hierarquia de memória, bem como as tecnologias de memória volátil e não volátil. O trabalho realiza experimentos comparando desempenho e consumo de soluções para SPM com memória volátil SRAM com soluções empregando modelos híbridos de memórias (SRAM, STT-RAM e PCM). Desta forma, este trabalho complementa os trabalhos existentes, pois, explora duas tecnologias de memória emergentes um único modelo de SPM.

## 1.3 Organização do Trabalho

O trabalho está dividido em seis capítulos. No segundo capítulo é realizada uma revisão dos aspectos dos dispositivos embarcados, suas principais características e restrições, além de apresentar uma revisão de hierarquias de memória, *caches* e *scratchpads*. Neste mesmo capítulo algumas tecnologias emergentes de memórias são revisadas, destacando suas respectivas características e as vantagens e desvantagens do uso de NVMs na hierarquia de memória.

No terceiro capítulo são revisadas as otimizações que podem ser realizadas, tanto em *hardware* quanto em *software*, ou em ambos para os sistemas de memória. Neste capítulo também são discutidos trabalhos relacionados que utilizam alguma dessas otimizações para a hierarquia de memória, incluindo trabalhos que exploram tecnologias emergentes.

No quarto capítulo é apresentada a metodologia adotada para a realização deste presente trabalho. Este capítulo apresenta as aplicações/*benchmarks* utilizados, a arquitetura avaliada e as ferramentas utilizadas para a realização do trabalho. No mesmo capítulo é apresentada a diferença entre as duas análises (estática e dinâmica) que são utilizadas ao decorrer do trabalho, com suas respectivas características, vantagens e desvantagens. Por fim, também são introduzidos os experimentos realizados neste trabalho.

No quinto capítulo são apresentados os resultados para os experimentos realizados, juntamente é realizada uma comparação dos resultados das abordagens estática e dinâmica. Neste capítulo, é possível identificar a influência das NVMs no consumo energético e no desempenho para os experimentos realizados. Por fim, o sexto capítulo apresenta as principais conclusões deste trabalho. Ainda neste capítulo são discutidos possíveis trabalhos futuros envolvendo NVMs em outros níveis hierárquicos de memória.

## 2 FUNDAMENTAÇÃO

Este capítulo apresenta conceitos e fundamentos importantes para a compreensão do trabalho. Primeiramente, o capítulo destaca características e restrições dos sistemas embarcados, além de revisar a hierarquia de memória em sistemas computacionais. Após, o capítulo discute algumas tecnologias emergentes de memórias.

### 2.1 Sistemas Embarcados

O desenvolvimento tecnológico dos últimos anos, como mencionado antes, trouxe consigo diversos aparelhos que auxiliam os seres humanos nas suas atividades diárias. Dentre estes equipamentos encontram-se: as máquinas que auxiliam nos afazeres domésticos, os aparelhos que auxiliam a medicina, podendo ajudar no controle dos pacientes ou até mesmo em cirurgias delicadas, os equipamentos que facilitam a comunicação das pessoas, ou para o entretenimento das mesmas, trazendo assim conforto e prazer para o seu dia-a-dia.

Segundo Marwedel (2011), sistema embarcado é um dispositivo no qual um sistema computacional é completamente encapsulado ou dedicado ao dispositivo ou equipamento que ele controla. Estes sistemas possuem uma funcionalidade restrita para atender uma tarefa específica em sistemas maiores nos quais estão inseridos. No mercado global 79% dos processadores utilizados são embarcados, certamente esse número deve ter sofrido um aumento significativo com os avanços dos anos, com a venda de dispositivos portáteis e produtos eletrônicos de consumo, como por exemplo, celulares, *smartphones*, televisores, câmeras digitais e DVD (*Digital Versatile Disc*). Estes processadores embarcados também podem ser encontrados em equipamentos maiores, como por exemplo, automóveis e aeronaves. Wolf (2012), destaca que um carro top de linha, ou seja, um carro com uma alta tecnologia, possui em torno de 100 processadores, enquanto um carro mais popular possui em média 60 processadores, representando assim, uma grande quantidade de eletrônica embarcada. Esses processadores são responsáveis pelo controle do

sistema de *air bag*, injeção eletrônica, ABS (*anti-lock braking system*), GPS, entre outros. No transporte aéreo são encontrados diversos dispositivos embarcados, presentes desde o controle da aeronave até os sistemas que possuem informações de cada passageiro. Muitos desses dispositivos embarcados precisam operar em tempo real para o correto funcionamento da aeronave, necessitam ser extremamente confiáveis, pois, são sistemas críticos que podem causar mortes e danos.

Com o avanço da tecnologia de semicondutores foi possível a integração de diversos sistemas mais complexos em um único chip (*system-on-chip – SoC's*), os mesmos serão cada vez mais necessários, devido ao fato do aumento da demanda de desempenho das diversas aplicações, como dispositivos portáteis, multimídia, entre outros. Os componentes de um SoC precisam ser específicos para cada domínio de aplicação, sendo que os elementos de processamento podem ser desde microcontroladores até microprocessadores, já por outro lado os componentes que fazem a comunicação dos elementos de controle podem ser *buffers*, memórias, barramentos, entre outros. Além disso, existe uma clara tendência dos sistemas embarcados serem implementados em SoC's, devido a integração de diversos componentes em um único chip, possibilitando assim a inserção de novas funcionalidades aos dispositivos portáteis. Essas novas funcionalidades agregadas aos dispositivos proporcionam um aumento significativo no consumo de energia, por isso, o mesmo tem sido enfrentado como um fator limitante às funcionalidades inseridas aos dispositivos alimentados por bateria.

Como visto, há uma diversa gama de aplicações onde sistemas embarcados estão envolvidos, e muitas delas possuem um grande número de funcionalidades que necessitam estar em um único dispositivo, um exemplo clássico é o celular de última geração ou *smartphones*. No mercado de *smartphones*, estão disponíveis diversos modelos de dispositivos com internet, câmera fotográfica, reproduutor de áudio e vídeo, *bluetooth*, entre outras funcionalidades. Outro exemplo é a eletrônica embarcada empregada atualmente em automóveis, como citado anteriormente, diversos processadores são responsáveis por controlar várias aplicações que estão inseridas nesses veículos, muitas dessas aplicações dependem dos resultados de diferentes sensores. Percebe-se assim, que os requisitos do sistema computacional por traz desses dispositivos são os mais diversos possíveis, portanto pode-se

afirmar que sistemas embarcados são naturalmente heterogêneos, pois são compostos de componentes de *hardware* (digital e analógico) e de *software*.

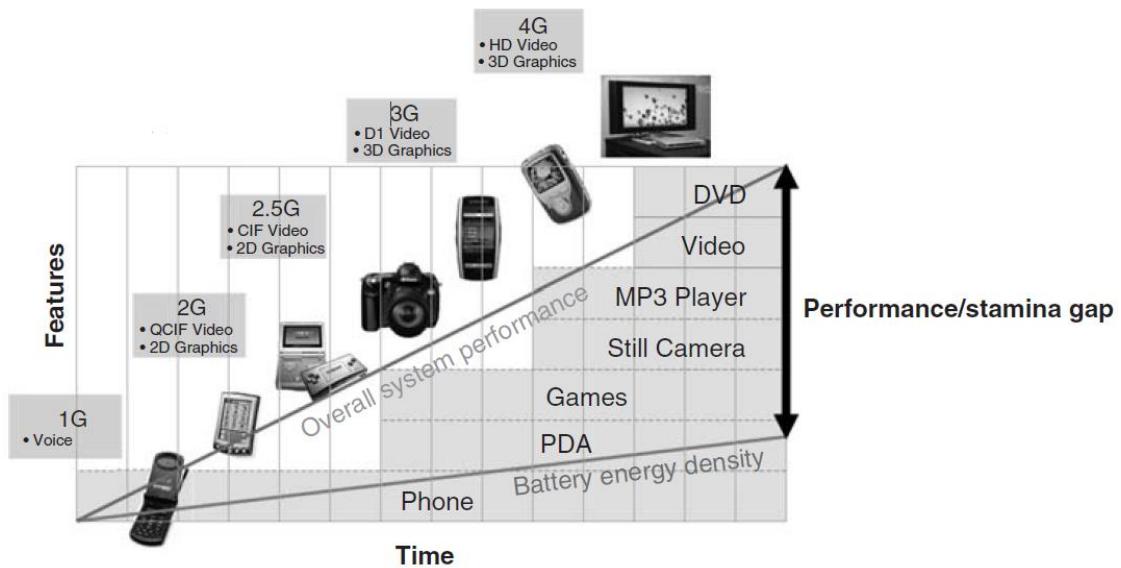

Em Shearer (2008), afirma-se que, a quantidade de recursos inseridos nos dispositivos portáteis teve um crescimento elevado se comparado com a tecnologia empregada na fabricação de baterias. Com isso, as funcionalidades agregadas consomem grande parte da energia fornecida pela bateria, diminuindo assim o tempo de utilização das mesmas. A Figura 4 mostra o aumento de recursos dos dispositivos embarcados em contraste com o consumo energético da bateria.

Figura 4 – Gap entre desempenho existente e energia.

Fonte: SHEARER, 2008.

Outro fator que chama a atenção é a exigência de dispositivos portáteis mais leves e menores, diminuindo assim o espaço destinado a bateria do dispositivo. Assim, um sofisticado gerenciamento de energia é a chave para aumentar o tempo de consumo das baterias, permitindo assim que o usuário do sistema disfrute ainda mais das funcionalidades oferecidas pelo dispositivo. Ou seja, o maior desafio encontrado é a realização de proporcionar o máximo desempenho em contraste com o mínimo gasto energético.

Os sistemas embarcados possuem muitas restrições e exigências, como por exemplo, baixo consumo de energia e potência, alto desempenho, tamanho e peso reduzidos. Os requisitos rígidos também são conhecidos como requisitos não funcionais, pois são frequentemente associados com o estado do sistema e não com as funcionalidades oferecidas como os requisitos funcionais. Estas e outras características possuem um forte impacto no projeto destes sistemas, tanto no ramo

de *software* quanto em *hardware*, no entanto, como destacado anteriormente, sistemas embarcados possuem uma vasta área de aplicações, onde cada uma pode ter características e requisitos diferentes. Como citado anteriormente em (WOLF, 2012) a descrição dos requisitos funcionais não é suficiente para o projeto de um sistema embarcado, devendo ser considerados também requisitos não-funcionais, tais como desempenho, custo, consumo de energia, tamanho físico e peso. Além das restrições físicas tradicionais, segundo Koopman (2007), sistemas embarcados são geralmente sistemas de segurança crítica, ou seja, a confiabilidade e a segurança são mais importantes do que o desempenho.

Algumas destas restrições são muito importantes no projeto de sistemas embarcados, tais como (MATTOS, 2007):

- Desempenho: com a crescente complexidade dos sistemas embarcados, a velocidade do sistema geralmente é requisito importante a ser alcançado;

- Tempo real: os sistemas embarcados geralmente estão envolvidos em tarefas onde os requisitos de tempo são rigorosos e devem responder a eventos externos, com uma avaliação precisa do tempo de execução;

- Dimensão física e peso: estes sistemas estão inseridos em sistemas maiores onde o requisito de portabilidade é muito importante, assim processadores embarcados devem ser pequenos e leves.

- Confiabilidade: alguns destes sistemas estão envolvidos em situações críticas onde os erros podem ter consequências dramáticas, envolvendo vidas humanas e enormes quantias de dinheiro;

- Tempo e custo de projeto: atualmente, o tempo de colocação do produto no mercado é muito importante. Assim, o tempo e custo de projeto devem ser reduzidos tanto quanto possível.

- Baixo consumo de energia: o consumo de energia apresenta uma questão crítica especialmente em dispositivos portáteis, pois estes utilizam bateria.

Como alegado anteriormente, sistemas embarcados são dedicados para uma determinada aplicação ao contrário dos dispositivos convencionais. No projeto de *hardware* para sistemas embarcados os fatores mais interessantes para serem

considerados são, o desempenho, custo (projeto e fabricação), tamanho físico, peso, consumo de energia e potência. Estes últimos são fatores limitantes na funcionalidade oferecida para alguns sistemas embarcados, principalmente os portáteis (SHEARER, 2008), que operam por bateria, como visto anteriormente, pois cada vez mais os dispositivos embarcados necessitam de mais funcionalidades, alto desempenho para um mesmo consumo energético.

## 2.2 Sistemas de Memória

Segundo Wolf e Kandemir (2003), a memória é um dos principais fatores de desempenho e consumo energético, portanto, o tamanho de memória é importante, principalmente nos dispositivos portáteis, visto que precisam possuir um tamanho pequeno de memória. Enquanto isso, os trabalhos de Catthoor et al. (2010), Verma e Marwedel (2007), e Hennessy e Patterson (2011) demonstram que a arquitetura de memória possui uma relevância importante em circuitos integrados, pois influenciam na área e no consumo energético do circuito. Como descrito por Catthoor et al. (2010), estas arquiteturas representam cerca de 40% a 60% do total de energia consumida por um processador embarcado para um conjunto de instruções.

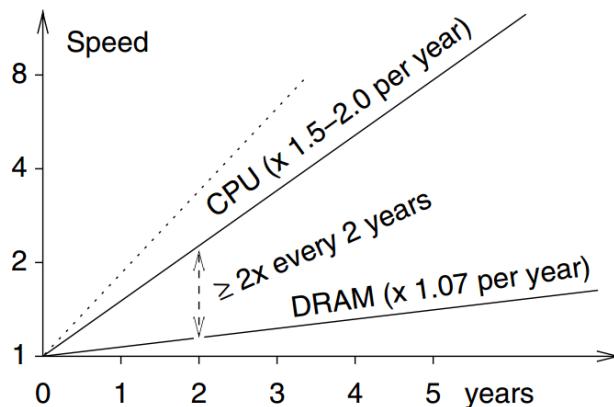

Em sistemas de computadores modernos, o principal empecilho para a obtenção de alto desempenho e eficiência energética, é a diferença tecnológica existente entre o desempenho do processador e da memória tradicional (HENNESSY e PATTERSON 2011), que é ainda mais significativa em sistemas embarcados. Enquanto a velocidade da memória DRAM está aumentando em um fator de 1,07 por ano, as velocidades dos processadores possuem um fator de aumento de 1,5 a 2 por ano (MARWEDEL, 2011). Atualmente, as velocidades dos processadores em relação as velocidades das memórias ainda estão aumentando, entretanto, essa diferença se comparada aos anos anteriores não possui o mesmo crescimento (Figura 3). Apesar disso a diferença de desempenho entre o processador e a memória é cada vez maior, conforme demonstrado na Figura 5, onde é apresentado o crescimento da velocidade do processador em contraste com o crescimento da velocidade da memória, com o passar dos anos. Com isso, é importante a utilização de memórias menores e mais rápidas, que atuem como um *buffer* entre a memória principal e o processador. Estas novas memórias são

inseridas na hierarquia de memória com o intuito de melhorar o desempenho entre o processador e a memória principal.

Figura 5 – Distância crescente entre as velocidades do processador e da memória.

Fonte: MARWEDEL, 2011.

Na literatura existe um leque muito grande de diversos tipos de otimizações de memória, as mesmas estão focadas não só em *hardware* ou *software*, mas podem ser uma combinação das duas abordagens, *hardware* e *software* como mencionado antes.

Em Acevedo e Jimenez (2002), mostra-se a contribuição de cada tipo de instrução para o consumo de energia do sistema. Dado um programa qualquer, conforme a instrução é chamada, partes específicas do microprocessador são ativadas, ou seja, a escolha correta da instrução poderia gerar uma redução do consumo de energia.

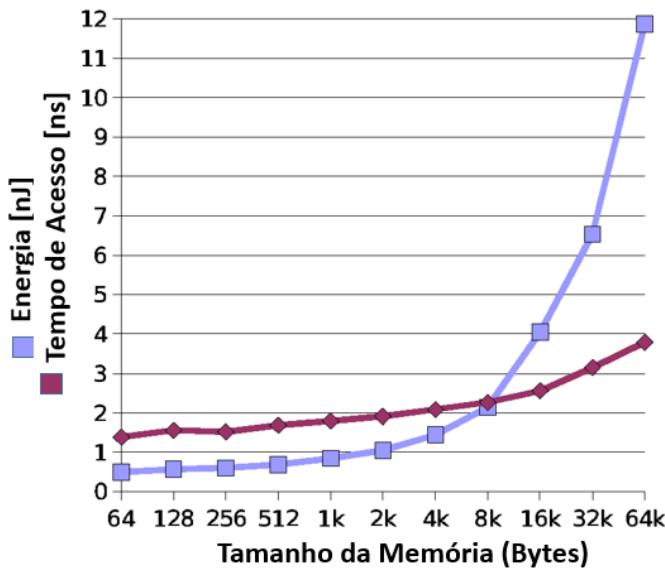

Os dados, informações, endereços e configurações devem ser armazenados em algum tipo de memória. No entanto, isto deve ser feito de alguma forma eficiente, para que a latência da busca do dado pelo processador seja a mínima possível, ou seja, o desempenho da busca deve ser o maior possível. Para melhorar o sistema original, realiza-se otimizações em código, ou até mesmo melhorias na hierarquia de memória. Possuindo assim resultados melhores em tempo de execução e eficiência energética, pois grandes memórias requerem mais energia para a busca do dado requerido pelo processador, além de demorarem mais tempo do que as memórias menores. A Figura 6 ilustra o tempo gasto para a busca de uma informação na memória, juntamente com a energia consumida, quando varia-se o tamanho de uma memória *cache* formada por SRAM. Pelo gráfico da Figura 6, percebe-se que a partir do ponto de 8k bytes haverá um aumento significativo no consumo energético, devido a fatores limitantes na tecnologia empregada para as memórias.

Figura 6 – Comportamento energético e tempo gasto em acesso a memória conforme o tamanho da mesma aumenta.

Fonte: MARWEDEL, 2014.

Existem praticamente dois tipos de memórias, as memórias não voláteis (NVM) e as memórias voláteis (VM). Como o próprio nome diz as memórias voláteis são aquelas que após o desligamento do sistema, ou seja, retirada a fonte de energia, perdem os dados armazenados, isto não acontece nas memórias não voláteis, onde quando é retirada a alimentação elas permanecem com os dados guardados. As memórias não voláteis são implementadas em muitos dispositivos embarcados, pois possuem características desejáveis, como por exemplo, tolerância a radiação, economia de energia e armazenamento dos dados garantidos, mesmo após o desligamento do aparelho (fonte de energia), sendo assim, não é necessária energia para manter os dados na memória, portanto, sua energia estática é muito pequena. Ainda as memórias não voláteis são mais densas do que as memórias voláteis, permitindo assim que, para uma mesma área de memória, os projetistas coloquem na memória não volátil uma quantidade maior de dados/informações.

### 2.2.1 Hierarquia de Memória

Os principais motivos para explorar o nível hierárquico das memórias é reduzir a energia gasta por acesso e o tempo do acesso à memória. Segundo Marwedel (2011), memórias maiores gastam mais energia por acesso e são mais lentas do que memórias menores. Com isso, busca-se obter uma boa eficiência

energética com um bom tempo de execução através da exploração hierárquica de memórias. Entretanto, o uso de memórias *caches* provocam alguns problemas para aplicações embarcadas, principalmente nas questões de previsibilidade. Além disso, as memórias rápidas possuem um custo elevado se comparado com memórias lentas, graças a isso uma hierarquia de memória é organizada em vários níveis, onde as memórias que possuem alta velocidade ficam nos níveis mais altos de processamento, e a cada nível abaixo, a memória é mais lenta. Sendo assim, tem-se no topo da hierarquia, perto do processamento, memórias de alta velocidade, entretanto com tamanho reduzido e de alto custo, e após, em cada nível desta hierarquia tem-se memórias maiores e custos decrescentes, entretanto possuem sua velocidade reduzida.

O conjunto de dados disponíveis na hierarquia mais alta é geralmente um subconjunto dos dados do nível inferior, e assim por diante. Desta forma, o objetivo é esconder as latências da memória não volátil e obter um sistema de alta velocidade de memória, através dos níveis utilizados na hierarquia de memória, com o menor custo possível, ou seja, busca-se um sistema de memória com a velocidade do nível superior possuindo um custo tão pequeno quanto o nível inferior. Os níveis de hierarquia de memória são implementados utilizando três tecnologias atualmente.

Primeiramente são encontradas as memórias que estão mais próximas ao processador, elas são chamadas de *caches*, utilizam a tecnologia de memória estática de acesso aleatório (SRAM). A tecnologia envolvida possui elevado desempenho para leituras e gravações, entretanto, é a tecnologia mais cara de toda a hierarquia de memória. Sendo assim, possui sua utilização em pequenos tamanhos, seguindo a tendência do mercado que quanto mais rápida, mais cara e menor. Além disso, esta memória é volátil, ou seja, não retém os dados quando desligada, necessitando permanecer sempre ligada para que seus dados sejam mantidos.

Posteriormente em um nível abaixo é encontrado as memórias principais de trabalho que utilizam a tecnologia DRAM, elas são maiores, mais lentas e mais baratas quando comparadas com as memórias *caches*. A memória do tipo DRAM, assim como a SRAM, precisa permanecer ligada para preservar seus dados.

O último nível de memória, conhecido como memória secundária, utiliza tecnologias de armazenamento não voláteis, ou seja, após o desligamento do sistema a memória irá manter os seus respectivos dados. Possuem um tamanho

total de armazenamento elevado, pois guardam uma grande quantidade de informações do sistema. Se faz necessário o emprego de uma memória deste tipo em pelo menos um nível da hierarquia de memória. As memórias deste nível geralmente utilizam meios magnéticos que são escritos e gravados por dispositivos mecânicos, esses dispositivos possuem um péssimo desempenho. Alternativamente, o último nível pode雇用memórias do tipo SSD (*solid-state drive*), elas sãmais rápidas quando comparadas com os meios magnéticos, entretanto, os SSD's possuem custos mais elevados.

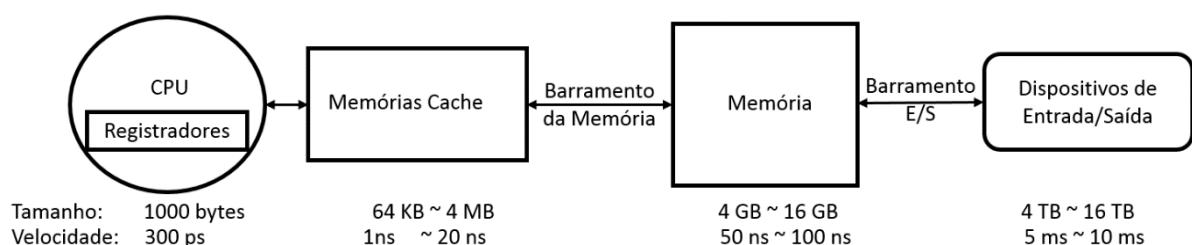

Os principais elementos que compõem uma hierarquia de memória são os registradores, a memória *cache*, a memória principal e a memória secundária. A Figura 7 apresenta uma ilustração com diferentes níveis de hierarquia de memória e seus respectivos tempos de acesso e tamanho físico.

O conceito de hierarquia de memória explora o princípio da localidade (HENNESSY e PATTERSON, 2011). Este princípio ocorre no tempo (localidade temporal) e no espaço (localidade espacial). O princípio pode ser visto como a necessidade do processador enxergar somente uma parte da memória durante a execução de uma aplicação, essa parte é referente aos dados e as instruções necessárias para a computação da tarefa ou aplicação. Este princípio ainda pode ser explicado, como sendo o comportamento dos programas em repetir trechos de código utilizando dados repetidos ou acessar repetidamente dados próximos aos que estão sendo utilizados. Sendo assim, o principal objetivo da hierarquia de memória é melhorar o desempenho.

Figura 7 – Diferentes níveis da hierarquia de memória em computadores embarcados, desktop e servidores.

Fonte: HENNESSY e PATTERSON, 2011.

O princípio de localidade pode ser classificado em dois tipos diferentes:

- Localidade Temporal: como o próprio nome diz, essa localidade se refere à necessidade temporal dos dados, ou seja, se um item é

referenciado, a probabilidade dele ser referenciado novamente é elevada. Sendo assim, existe a necessidade de manter os dados recentemente acessados na hierarquia que está mais próxima ao processador.

- Localidade Espacial: a mesma é referente ao local de armazenamento da memória, ou seja, se um item é referenciado, os itens de endereços próximos possuem a probabilidade de serem referenciados em breve. Sendo assim, existe a necessidade de não apenas trazer para a hierarquia mais próxima ao processador os dados referenciados, mas sim o bloco de dados, que contém os dados de endereços próximos.

### **2.2.2 Caches**

São chamadas de memórias *caches*, as hierarquias de memórias que estão localizadas entre o processador e a memória principal de trabalho, ou seja, geralmente são memórias que estão perto dos processadores. Atualmente os computadores de uso geral possuem pelo menos um nível de hierarquia de *cache*.

O funcionamento das memórias *caches* pode ser definido em dois passos, dado um endereço de acesso, que foi gerado pelo processador para a busca de algum dado na memória. Primeiramente a *cache* irá verificar se possui uma cópia da posição de memória solicitada do processador, se possuir, ela verificará a posição correspondente dentro da *cache* que contenha o endereço solicitado e o retornará ao processador, caso contrário, se a *cache*, não possuir o endereço solicitado, ela irá trazer o conteúdo da memória principal e escolherá uma posição onde a cópia do dado será armazenado, e retornará uma cópia ao processador.

### **2.2.3 Scratchpads**

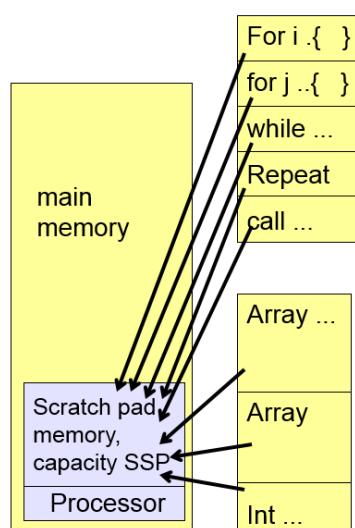

Uma memória *scratchpad* (SPM) é um *array* de memória com a parte de lógica de decodificação (BANAKAR, et al., 2002). A ideia por traz de uma *scratchpad* é manter objetos de memória mapeados pelo compilador no seu último estágio. A SPM ocupa uma parte do espaço de endereçamento e o restante é ocupado pela memória principal.

A grande vantagem das SPM's é que não existe necessidade de checagem da disponibilidade do dado ou instrução como nas memórias *caches*, eliminando o emprego de rótulos (*tags*) e comparadores existentes nas *caches*. Isso contribui significativamente na redução da área e consumo de energia. Segundo Banakar et al. (2002) uma cache utilizando memória SRAM normalmente possui um consumo energético entre 25% a 45% do consumo total do chip. Os autores utilizaram uma memória *scratchpad* com o objetivo de reduzir o consumo de energia e de área, os resultados do trabalho de Banakar et al. (2002), apresentaram uma redução de 40% no consumo energético e uma redução em média de 46% na área. Assim, a memória *scratchpad*, tem sido amplamente adotada em muitos sistemas embarcados devido a sua menor área e menor consumo energético. Além disso, a *scratchpad* pode proporcionar muitas vezes uma melhor previsibilidade e sincronização em dispositivos de tempo real, por ser uma memória gerenciada por software (LI, GAO e XUE, 2005).

A memória *scratchpad* apesar de ser uma técnica de otimização de memória por *hardware*, pode possuir também técnicas com abordagens em *softwares*. O trabalho de (LI, GAO e XUE, 2005) propõe uma metodologia para o problema de gerenciamento de memória *scratchpad*, o qual pode ser resolvido por um algoritmo de coloração de grafos para a alocação de registradores.

Uma *scratchpad* pode conter instruções ou dados alocados em seu interior. A Figura 8 demonstra as informações que podem ser alocadas em uma *scratchpad* em uma determinada hierarquia de memória.

Figura 8 – Exemplo de alocação de dados/instruções em uma *scratchpad*.

Fonte: MARWEDEL, 2014.

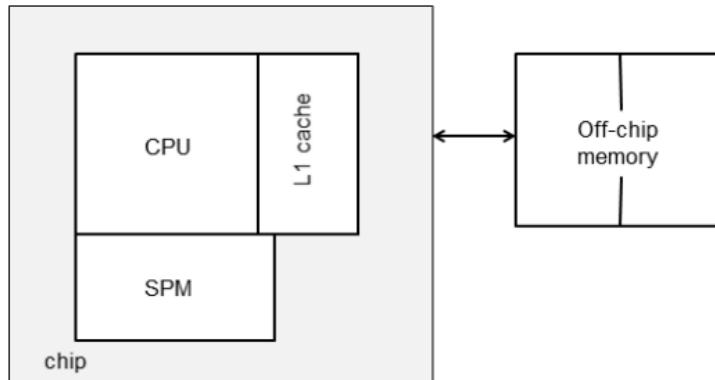

A Figura 9 demonstra um sistema embarcado genérico com as memórias *on-chip* e *off-chip*. O sistema de memória principal pode estar contido parcialmente dentro do chip (*on-chip*) e parcialmente fora do chip (*off-chip*). A maioria dos sistemas embarcados utiliza somente um único nível de *cache*, como observado na Figura 9, porém com a necessidade de aumento de desempenho, podem existir outros níveis de *cache*.

Pela Figura 9, as memórias *scratchpads* (SPM) podem ser utilizadas juntamente com memórias *caches*, como memórias de alta velocidade *on-chip*. O tipo tradicional de memória empregada nas SPMs e *caches* são as memórias SRAMs. Na forma *off-chip*, memórias de tecnologias diversas podem ser utilizadas, inclusive memórias SDRAM (*Synchronous Dynamic Random-Access Memory*) ou RDRAM (*Rambus Dynamic Random-Access Memory*). As memórias *on-chip* e *off-chip* influenciam o desempenho e o consumo de energia em sistemas embarcados.

Figura 9 – Vista centrada em memória de um sistema computacional embarcado.

Fonte: WOLF e KANDEMIR, 2003.

### 2.3 Tecnologias Emergentes em Memórias

Com o avanço da tecnologia, a memória tradicional baseado em SRAM *on-chip* tornou-se um gargalo para o projeto de eficiência energética em sistemas embarcados, devido ao seu alto *leakage* (corrente de fuga) e tempo de acesso. As tecnologias emergentes de memória não volátil, tal como STT-RAM, PCRAM, RRAM e DWM são as possíveis soluções para os sistemas de memória futuras.

No trabalho de Mittal, Vetter e Li (2015), os autores realizam um breve resumo das tecnologias de memória e classificaram diversos trabalhos que utilizam essas

memórias em seus experimentos, na Seção 2.3.1 encontra-se um resumo destas tecnologias juntamente com as suas características e os desafios na sua utilização.

### **2.3.1 Embedded DRAM**

*Embedded* DRAM, ou (eDRAM, do inglês, *Embedded Dynamic Random-Access Memory*) é uma RAM dinâmica baseada em um capacitor que pode ser integrado no mesmo molde que o processador. Este modelo pode conter um capacitor e um transistor (1T1C) convencional DRAM na célula, ou uma lógica compatível de ganho celular (CHANG, et al., 2013) e (AGRAWAL, et al., 2013), ambos usam alguma forma de capacitor para armazenar os dados. Como a carga armazenada vazia gradualmente, a atualização periódica é necessária para preservar seu valor e evitar a decadência.

A exigência da atualização periódica é dos maiores obstáculos no uso de eDRAM. Estas memórias empregam transistores de lógica rápidos, que possuem um *leakage* maior do que a DRAM convencional e, portanto, sua exigência de atualização também é maior do que da DRAM. Em Barth et al. (2008) os autores relatam que o período de retenção da eDRAM é de 40 ms, em comparação com o período de retenção de 64ms de uma DRAM tradicional (WILKERSON, et al., 2010). Além disso, o período de retenção da informação reduz ainda mais devido a fatores como o aumento da temperatura, processo de variação e dimensionamento da tecnologia (CHANG, et al., 2013) e (ALIZADEH, et al., 2012). Atualizar as operações consome uma fração significativa do consumo energético da *cache*, além de interferir no acesso da *cache* e reduzir a disponibilidade da *cache*. Além disso, para pequenos períodos de retenção e *caches* de grandes dimensões, um número muito grande de blocos precisa ser atualizado em uma pequena quantidade de tempo. A eDRAM é criticada por possuir desafios de escalabilidade devido à dificuldade de colocação de carga precisa e dados de sensoriamento. Por fim, uma memória *cache* de 4MB empregando eDRAM possui como latência de leitura/gravação um intervalo entre 3 e 5 nanosegundos (CHANG, et al., 2013) e (CACTI, 2014).

### **2.3.2 STT-RAM**

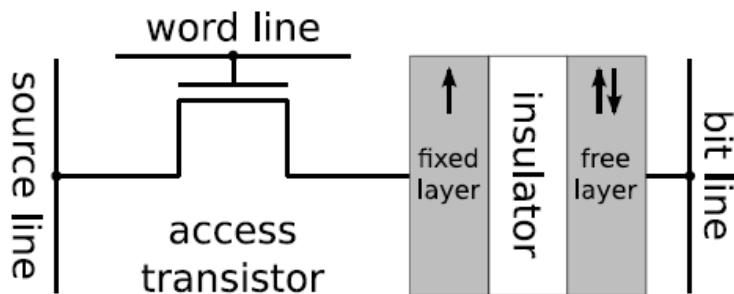

Segundo Smullen et al. (2011), a STT-RAM utiliza uma junção de túnel magnético (*Magnetic Tunnel Junction*, MTJ) como armazenamento de memória. A

Figura 10 exibe uma célula STT-RAM, nota-se pela figura que um transistor de acesso é ligado a um elemento de memória implementado usando um MTJ, que contém duas camadas ferromagnéticas separadas por uma camada isoladora de óxido. A direção da magnetização de uma camada ferromagnética é fixa enquanto que a outra camada ferromagnética pode ser alterada pela passagem de uma corrente. A resistência do MTJ é determinada pela direção de magnetização relativa dessas duas camadas. Se as duas camadas têm direções diferentes, a resistência do MTJ é alta e vice-versa. Usando essa propriedade, um valor binário é armazenado em uma célula STT-RAM. Para ler o valor armazenado, uma pequena tensão é aplicada entre os terminais MTJ. A corrente que flui através do dispositivo é detectada, e o estado de magnetização é determinado como um resultado.

Figura 10 – Célula STT-RAM.

Fonte: RODRÍGUEZ, TOURIÑO e KANDEMIR 2014.

Embora a STT-RAM possua densidade menor do que a PCM e a RRAM, e maior latência e energia para a operação de escrita do que a SRAM, essa memória foi amplamente utilizada para a concepção de *caches* devido a seu alto *endurance*. O *endurance* é o número de ciclos de gravações que podem ser aplicados a um bloco de memória *flash*, antes que a mídia de armazenamento torne-se inconfiável. No entanto, apesar de um valor de *endurance* de  $10^{15}$  foi estimado, o melhor resultado do teste de *endurance* até agora é inferior a  $4 \times 10^{12}$  (HUAI, 2008). Outra vantagem da STT-RAM é que a sua não-volatilidade pode ser negociada para melhorar sua energia de gravação e latência.

Em Smullen et al. (2011), os autores modificam o tempo de retenção encolhendo a área planar do MTJ, enquanto que o trabalho de Jog et al. (2012) consegue isto diminuindo a espessura da camada livre e baixando a saturação da magnetização que reduz a barreira térmica do MTJ. Como exemplo, Jog et al. (2012)

mostra que para a frequência de 2 GHz, os valores de latência de gravação de uma STT-RAM de 4 MB para períodos de retenção de 10 anos, 1 segundo e 10 milissegundos são respectivamente 22, 12 e 6 ciclos. Assim, com base na característica da aplicação e no nível da hierarquia da *cache*, um *designer* pode escolher um valor apropriado de período de retenção.

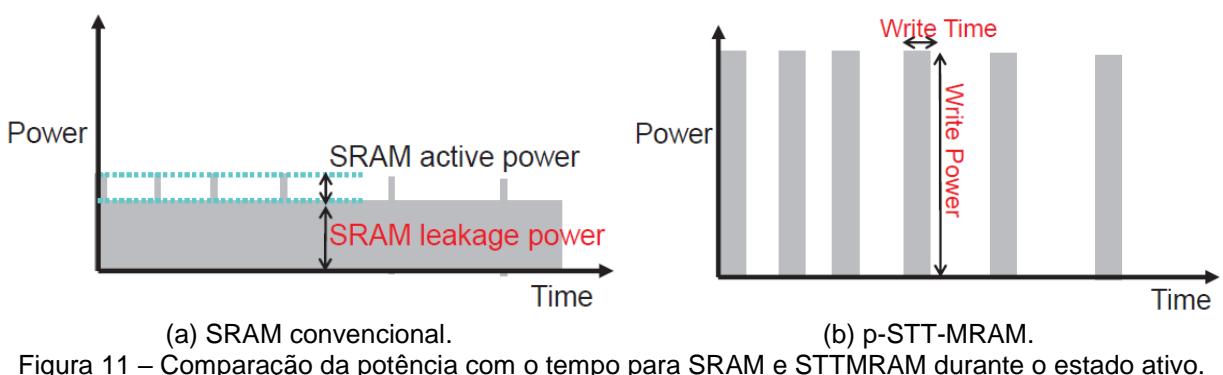

O modelo de memória p-STT-RAM (*Perpendicular Spin-Transfer Torque Magnetic Random-Access Memory*) possui uma maior probabilidade para substituir a SRAM do que a STT-MRAM, pois a p-STT-RAM apresenta uma maior velocidade de acesso. Com os avanços da tecnologia CMOS, com a fabricação de transistores cada vez menores, o *leakage* da SRAM cresceu consideravelmente, tornando-se uma parte significativa do consumo energético total em diversos chips de semicondutores. A Figura 11 (a) mostra a energia típica de uma SRAM durante o estado ativo, indicando que a energia total gasta por uma SRAM é predominantemente o *leakage*. Como mostrado na Figura 11 (b), idealmente, não há *leakage* para STT-MRAM. No entanto, para reduzir a energia total (energia total = ativa + *leakage*, na Figura 11), substituindo uma SRAM por uma p-STT-MRAM, o ponto mais importante é a redução no consumo energético e/ou a redução da latência para operações de escrita da STT-MRAM.

Figura 11 – Comparação da potência com o tempo para SRAM e STTMRAM durante o estado ativo.

Fonte: FUJITA et al., 2015.

### 2.3.3 RRAM

Uma RRAM com comutação unipolar usa um dielétrico isolador (LI e CHEN, 2009). Quando é aplicada uma tensão suficientemente elevada, é formado um filamento ou um percurso condutor no dielétrico isolador. Depois disso, aplicando

tensões adequadas, o filamento pode ser ajustado para *set* (o que leva a uma baixa resistência) ou *reset* (o que leva a uma alta resistência).

Comparado a SRAM, uma cache RRAM tem alta densidade, latência de leitura comparável e possui um valor muito inferior de gasto energético referente ao *leakage*. No entanto, as limitações da RRAM são a seu baixo *endurance*, cerca de  $10^{11}$  (KIM, et al., 2011), alta latência e consumo energético para as operações de escrita. Por exemplo, uma cache típica de 4 MB de RRAM tem uma latência de leitura entre 6 e 8 nanosegundos e uma latência de escrita entre 20 e 30 nanosegundos (DONG et al., 2012).

### 2.3.4 PCM

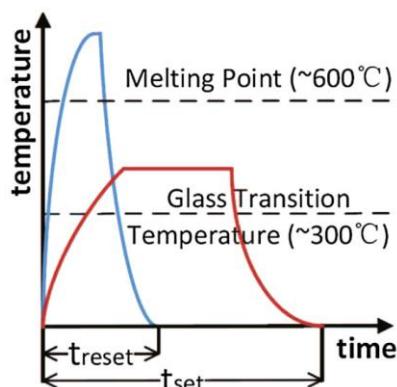

A PCM usa um material de mudança de fase chamado GST, que é uma liga de germânio, antimônio e telúrio. Quando a liga é aquecida a uma temperatura muito alta e rapidamente resfriada, transita em uma substância amorfa com alta resistência elétrica (*reset*). Por outro lado, quando a liga é aquecida a uma temperatura entre a cristalização e o ponto de fusão e resfriada lentamente, cristaliza até um estado físico com menor resistência (*set*). A Figura 12 ilustra as operações *set* e *reset*. Na Figura 12 para a operação *set*, quando o GST é aquecido a uma temperatura entre a temperatura de cristalização (~ 300 ° C) e a temperatura de fusão (~ 600 ° C) durante um período de tempo, GST transforma-se no estado cristalino que corresponde a um Lógica '1'. Para a operação *reset*, quando o GST é aquecido acima do ponto de fusão e extinguido rapidamente, GST transforma-se no estado amorfo que corresponde ao '0' lógico. Esta propriedade física é usada para armazenar um valor binário em uma célula PCM.

Figura 12 – As operações *set* e *reset* da PCM.

Fonte WANG et al., 2015.

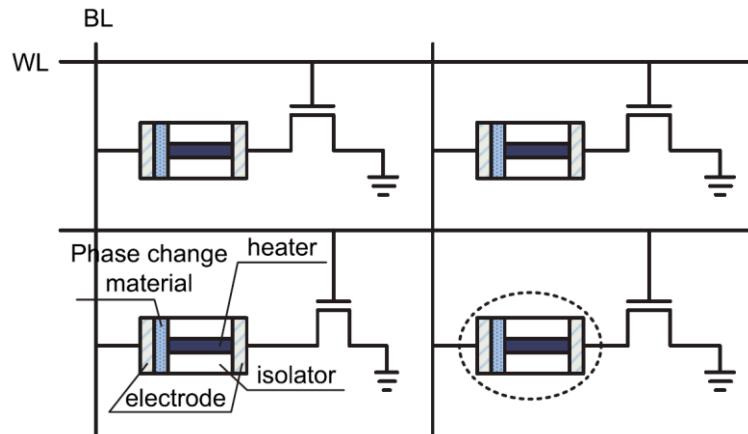

Em um chip PCM, as células são organizadas na matriz bidimensional tal como ilustrado na Figura 13. Nesta figura percebe-se a estrutura básica de uma célula da PCM, essa estrutura consiste em um transistor NMOS e um dispositivo de mudança de fase.

Figura 13 – Uma matriz de células PCM e a estrutura de uma célula PCM.

Fonte: WANG et al., 2015.

Os dois desafios mais graves no uso de PCM para projetar *caches on-chip* são sua resistência limitada de escrita e alta latência de gravação. Uma vez que o tráfego de escrita para uma *cache* é muito mais pesado do que para uma memória principal e a *endurance* da PCM é apenas perto de  $10^8$  escritas (WANG, et al., 2013) e (JOO, et al., 2010), para diversas aplicações, uma *cache* que utiliza PCM pode falhar em menos de uma hora. Uma típica *cache* de 4 MB utilizando PCM possui uma latência de leitura entre 15 e 20 nanosegundos e uma latência de escrita entre 150 e 170 nanosegundos (DONG et al., 2012) e (JOO, et al., 2010). Assim, a PCM é adequada para a memória principal ou hierarquias inferiores de *cache*, por exemplo, *cache* L3 ou mesmo *cache* L4 (WU, et al., 2009), onde a sua latência elevada pode ser tolerada e a alta densidade pode ser utilizada para evitar acessos fora do chip.

### 2.3.5 DWM

A DWM funciona controlando a parede do domínio (*Domain Wall*, DW) em nanofios ferromagnéticos (VENKATESAN, et al., 2012). O fio ferromagnético pode ter múltiplos domínios que são separados por paredes de domínio. Esses domínios podem ser individualmente programados para armazenar um único bit (na forma de

uma direção de magnetização) e assim, o DWM pode armazenar múltiplos bits por célula de memória.

Logicamente, uma macrocélula DWM aparece como uma fita, que armazena múltiplos bits e pode ser deslocada em qualquer direção. O desafio na utilização de DWM é que o tempo consumido no acesso a um bit depende da sua localização em relação à porta de acesso, o que leva a uma latência de acesso não uniforme e torna o desempenho dependente do número de operações de deslocamento necessárias por acesso. Comparado com outras NVMs, DWM é mais recente, e ainda está em fase de pesquisa e protótipos.

### **2.3.6 Comparativo entre as Tecnologias Emergentes**

Ao contrário de memórias baseadas em carga, como DRAM, NVMs armazenam seus dados através da mudança do estado físico. Uma vez que uma operação de escrita para NVM envolve a mudança de seu estado físico, uma operação de gravação para NVM possui maior latência e consumo energético do que uma operação de leitura, levando a assimetria leitura-escrita (BISHNOI, et al., 2014a). Da mesma forma, a latência de escrita e o consumo energético da transição da lógica 1 para 0 é maior do que a de 0 para 1, levando a assimetria de escrita de 0/1 (BISHNOI, et al., 2014b). As NVMs também permitem o armazenamento de múltiplos bits de dados em uma única célula de memória. Isto é referido como armazenamento de células de múltiplos níveis (*Multi-Level Cell*, MLC) e conduz a um aumento significativo na densidade de armazenamento das NVMs.

Comparando com a memória tradicional SRAM, as memórias emergentes STT-RAM e PCRAM proporcionam um *leakage* menor e uma maior densidade. Comparando-as entre si, STT-RAM possui uma menor latência de acesso e potência dinâmica, enquanto PCRAM possui maior densidade. Segundo Wu et al. (2009) e Sun et al. (2009) a memória STT-RAM é mais adequada para memórias de último nível, enquanto que a PCRAM é promissora como uma alternativa para DRAM na memória principal (LEE, et al., 2009).

Embora STT-RAM apresente muitas características atraentes, como o baixo *leakage* e alta densidade, esse tipo de memória possui alguns problemas. Ao contrário da SRAM, em que ler e escrever operações consomem o mesmo tempo e energia, uma operação de gravação de STT-RAM precisa de muito mais tempo de

latência e maior energia do que uma operação de leitura. Além disso, a latência e a energia de operações de escrita convencionais em uma STT-RAM são várias vezes maiores do que os da SRAM para um mesmo tamanho de memória. Como a memória *on-chip* é mais próxima à CPU na hierarquia de memória, reduzir a latência de acesso a memória *on-chip* é fundamental para o aumento do desempenho em sistemas embarcados.

Novos modelos de STT-RAM foram desenvolvidos para diminuir os problemas envolvidos com as operações de escrita. Segundo Khalili et al. (2011) e Tadisina et al. (2010), as PMTJ (*Perpendicular Magnetic Tunnel Junction*) foram desenvolvidas para alcançar uma baixa corrente de comutação, mantendo uma alta estabilidade térmica para as STT-RAM. Já em Xu et al. (2011), os autores conseguiram diminuir significativamente os problemas de gravação em STT-RAM SPM, graças a um cuidadoso processo de cootimização entre os dispositivos da arquitetura.

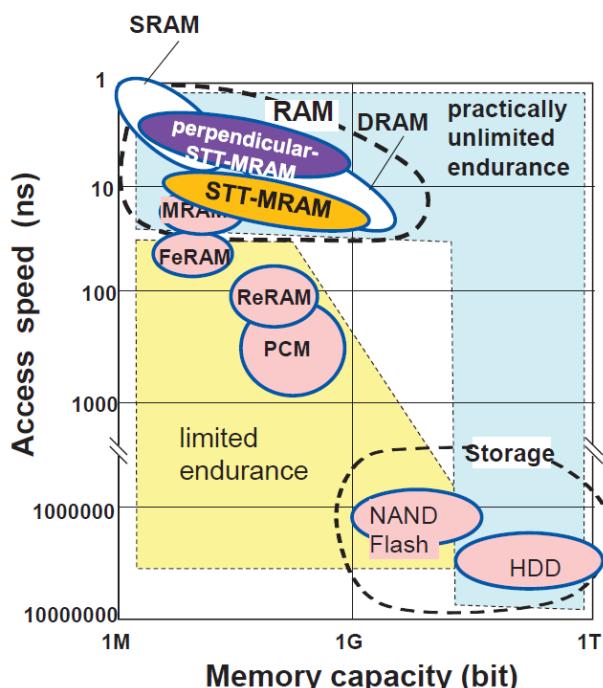

A Figura 14 exibe a capacidade, a velocidade dos acessos e o *endurance* de diversos modelos de memórias. Nesta figura nota-se modelos de memórias com acessos rápidos como SRAM, STT-RAM, p-STT-RAM e DRAM, com acessos moderados como PCM e ReRAM e com acessos lentos, como por exemplo, discos rígidos e memória flash. Observa-se que o modelo p-STT-RAM possui velocidade de acesso a memória superior ao modelo STT-RAM.

Figura 14 – Capacidade e velocidade de acesso de diversas memórias.

Fonte: FUJITA et al., 2015.

O trabalho de Mittal, Vetter e Li (2015), apresenta uma avaliação comparativa das propriedades das diferentes tecnologias de memórias (Tabela 1). Os valores apresentados podem não ser satisfatórios, entretanto com a pesquisa contínua, os valores das propriedades podem ser melhorados significativamente.

Tabela 1 – Características das diferentes tecnologias de memórias

|                             | SRAM        | EDRAM            | STT-RAM               | RRAM        | PCM               | DWM         |

|-----------------------------|-------------|------------------|-----------------------|-------------|-------------------|-------------|

| Tamanho da Célula ( $F^2$ ) | 120 - 200   | 60 – 100         | 6 - 50                | 4 - 10      | 4 - 12            | > 2         |

| Endurance                   | $10^{16}$   | $10^{16}$        | $4 \times 10^{12}$    | $10^{11}$   | $10^8 - 10^9$     | $10^{16}$   |

| Velocidade (L/E)            | Muito Veloz | Veloz            | Veloz/Lento           | Veloz/Lento | Lento/Muito Lento | Veloz/Lento |

| Leakage                     | Alto        | Médio            | Baixo                 | Baixo       | Baixo             | Baixo       |

| Energia Dinâmica (L/E)      | Baixo       | Médio            | Baixo/Alto            | Baixo/Alto  | Médio/Alto        | Baixo/Alto  |

| Período de retenção         | N/A         | 30 - 100 $\mu$ s | N/A (Quando Relaxado) | N/A         | N/A               | N/A         |

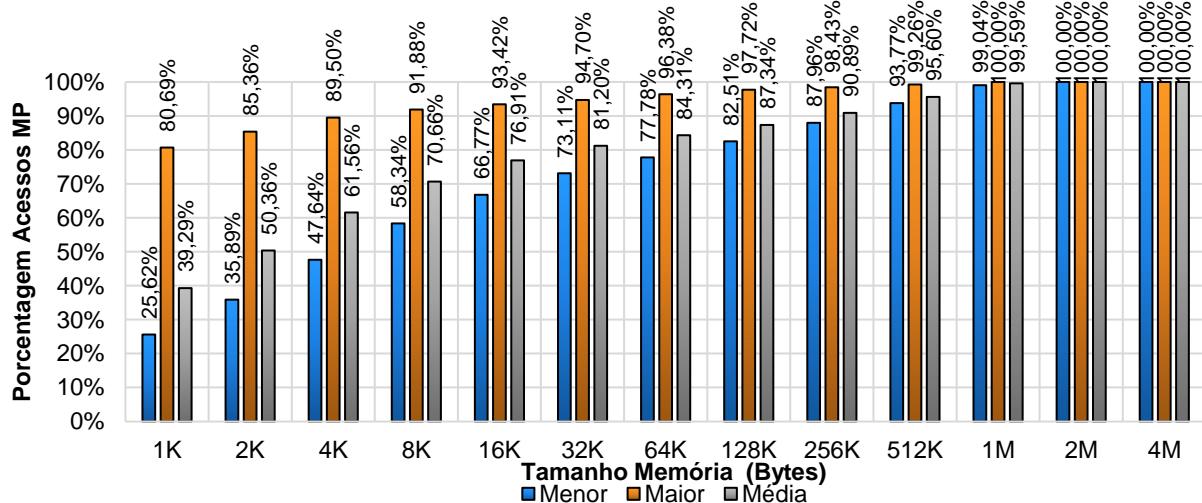

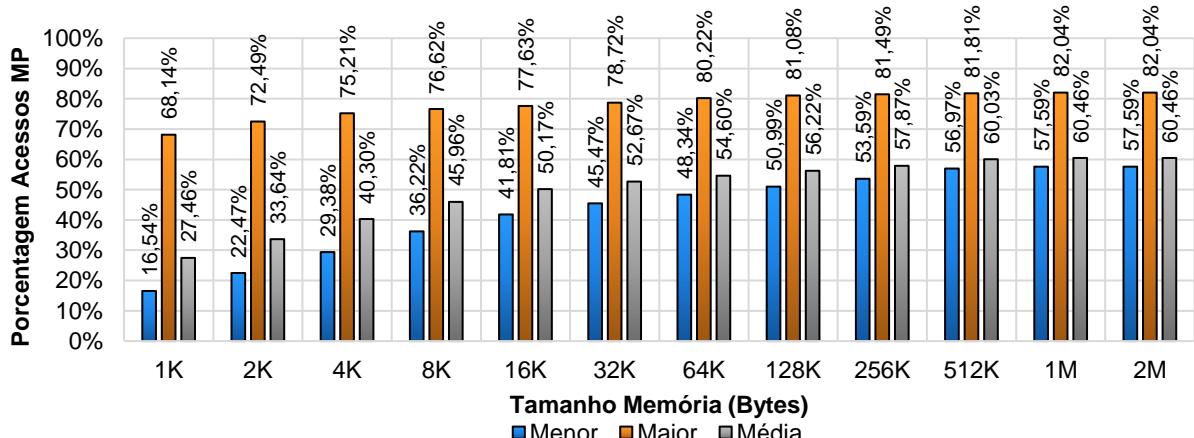

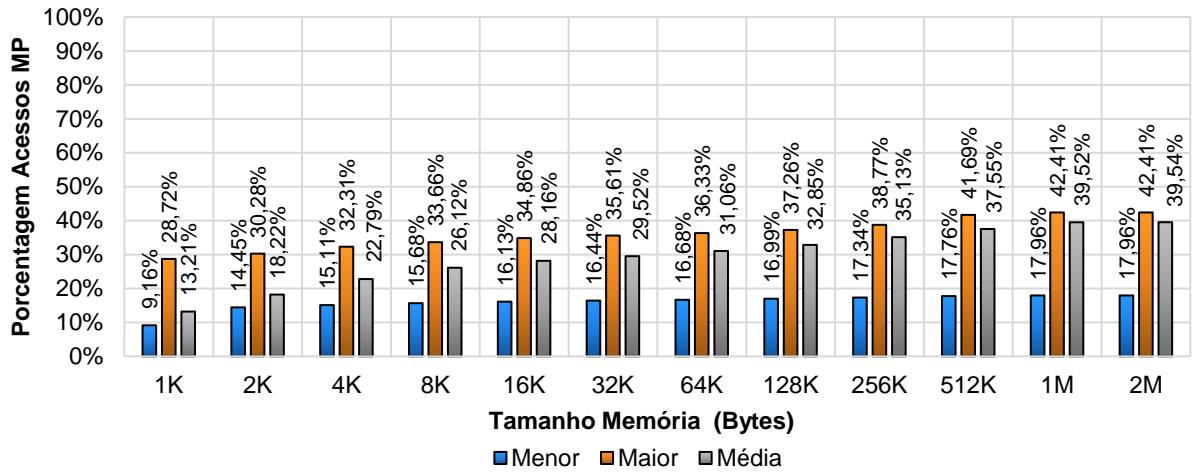

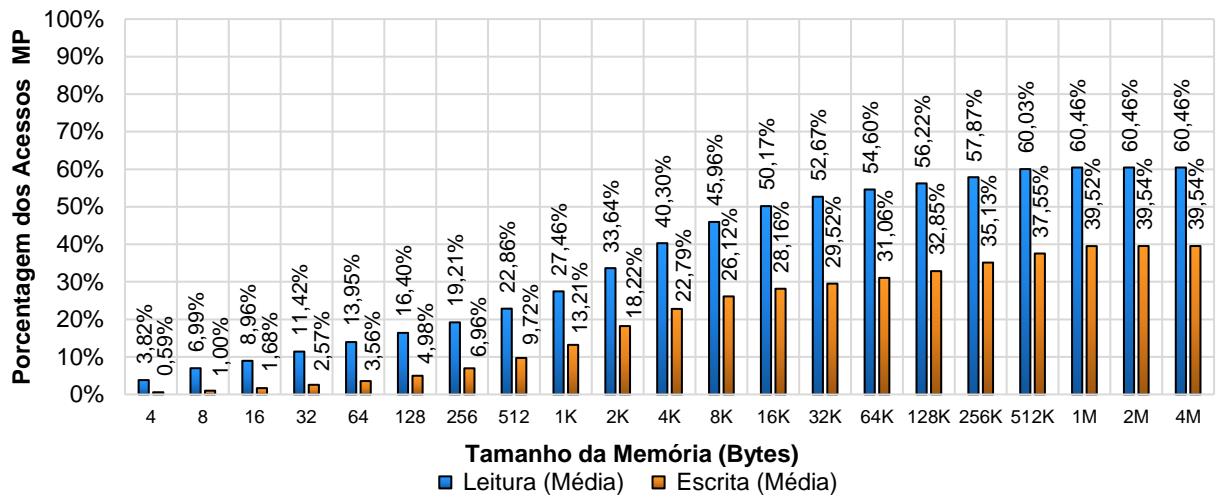

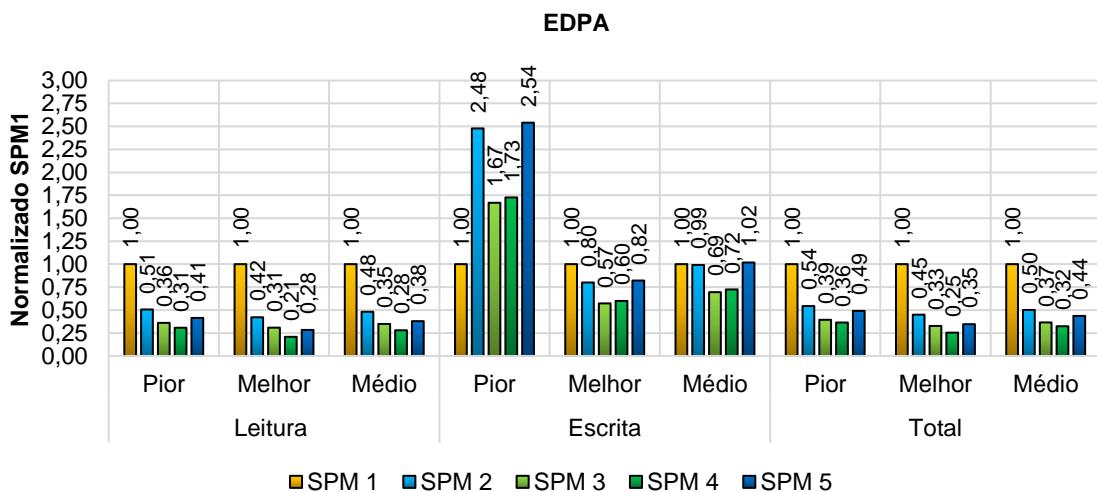

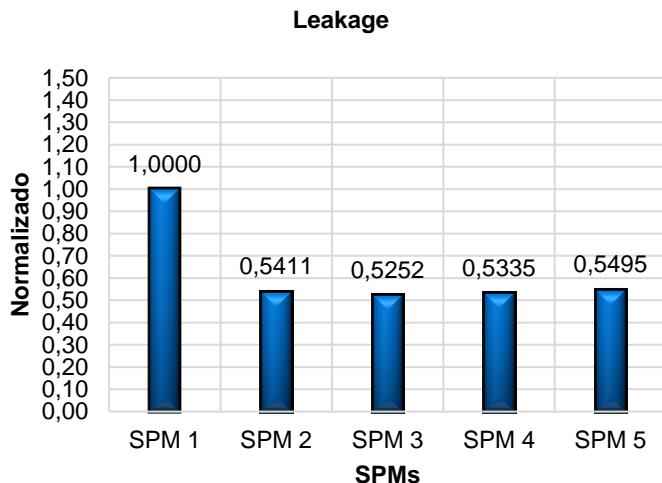

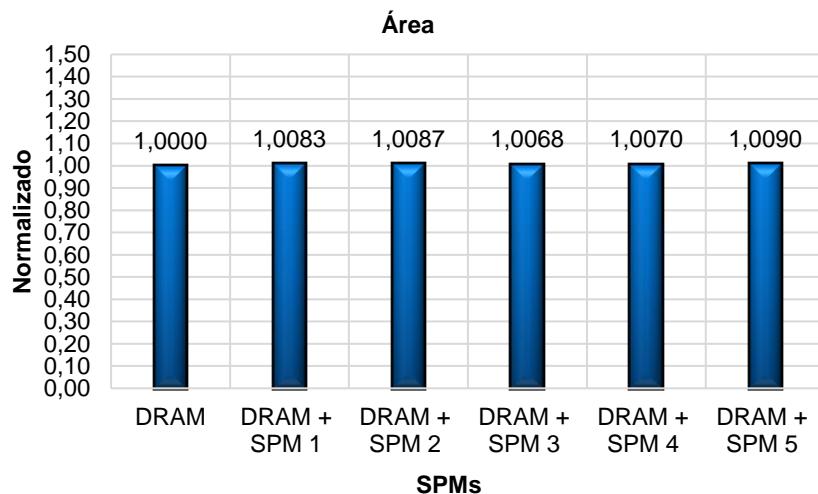

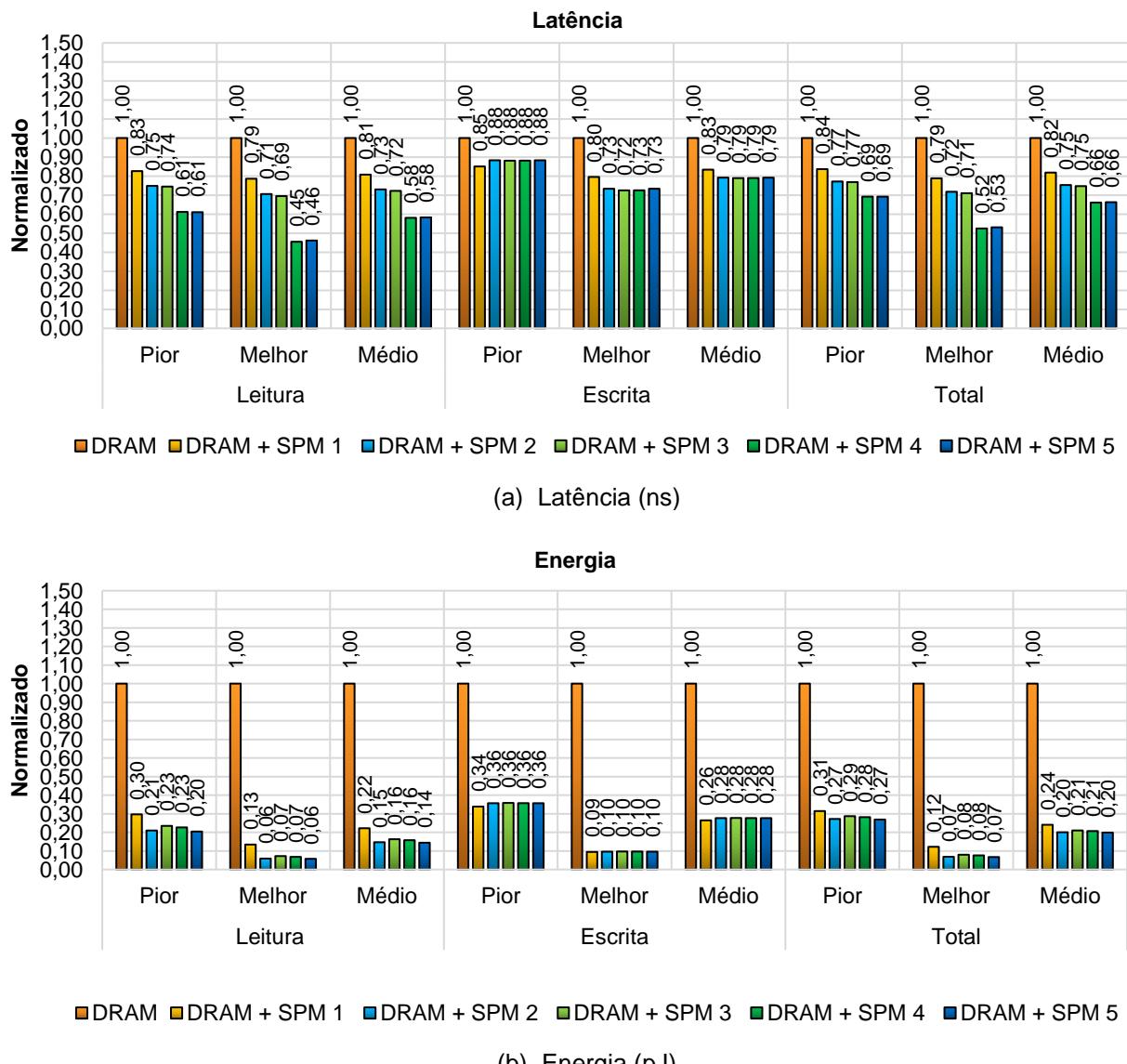

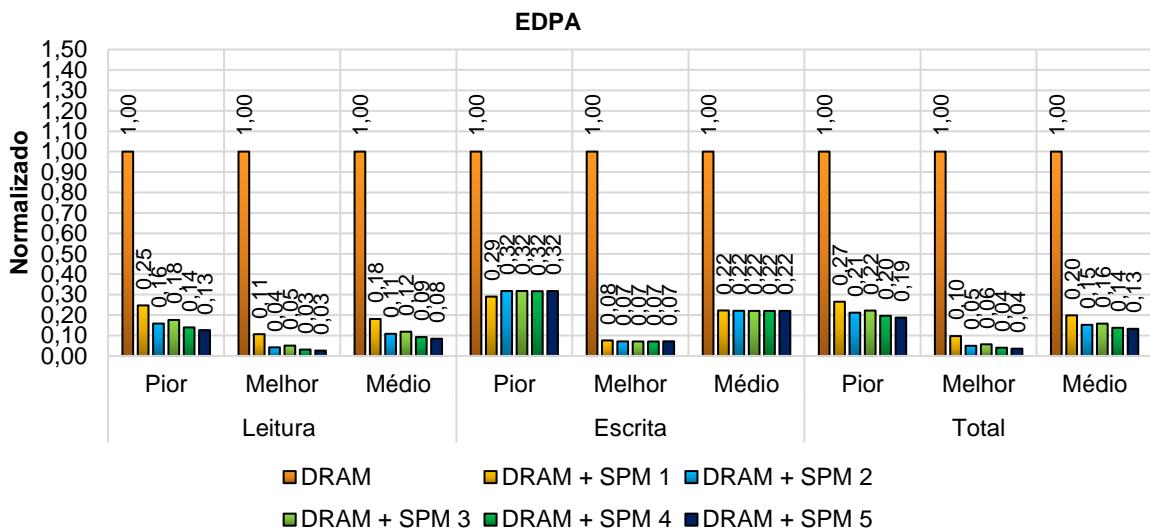

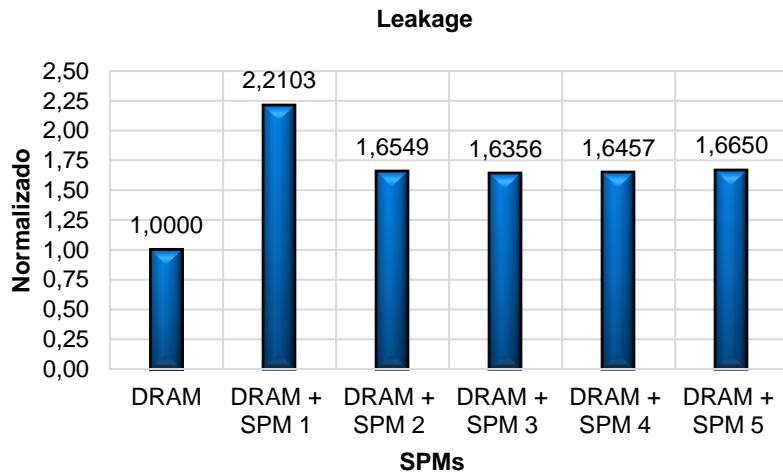

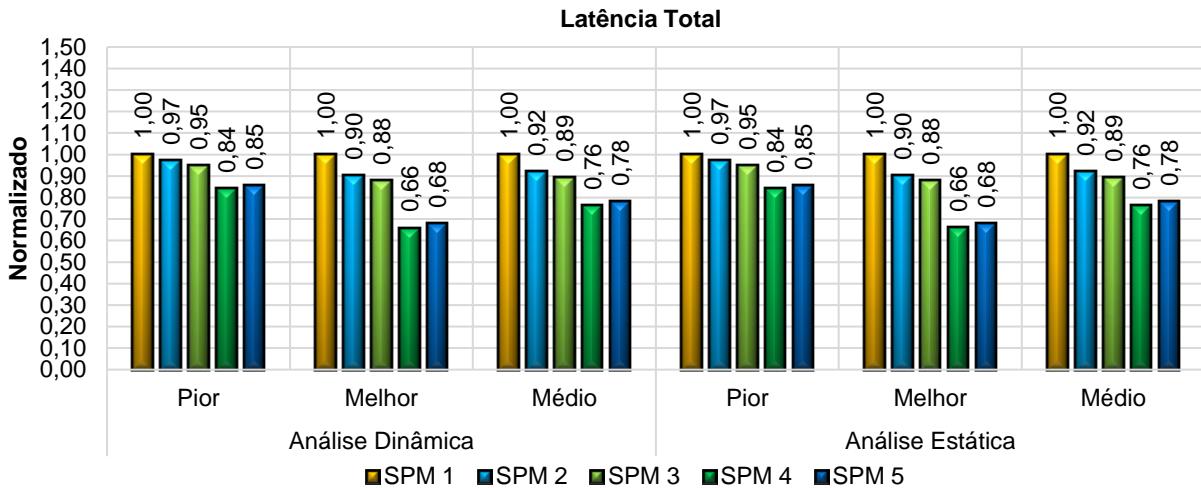

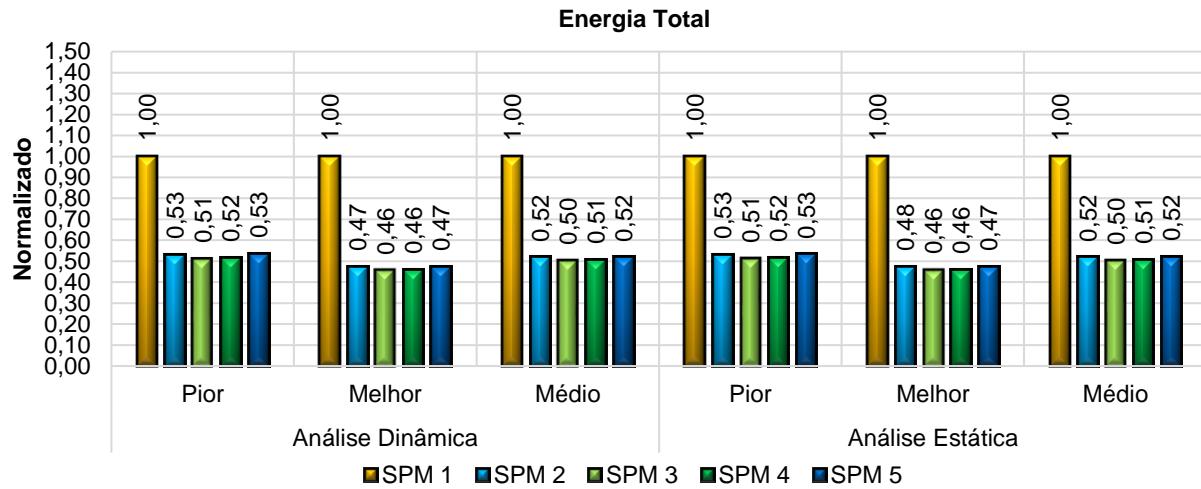

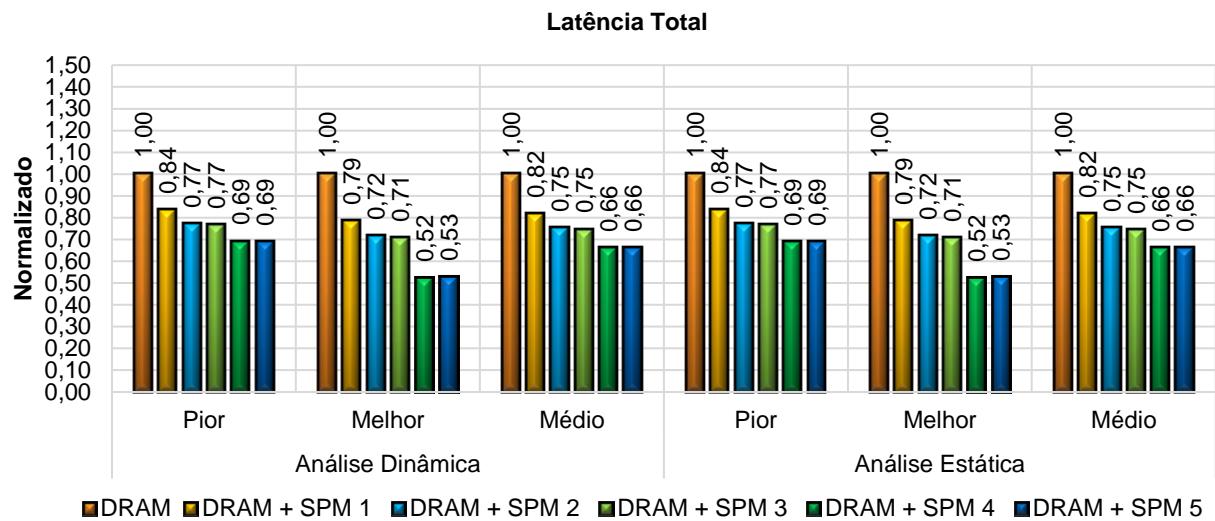

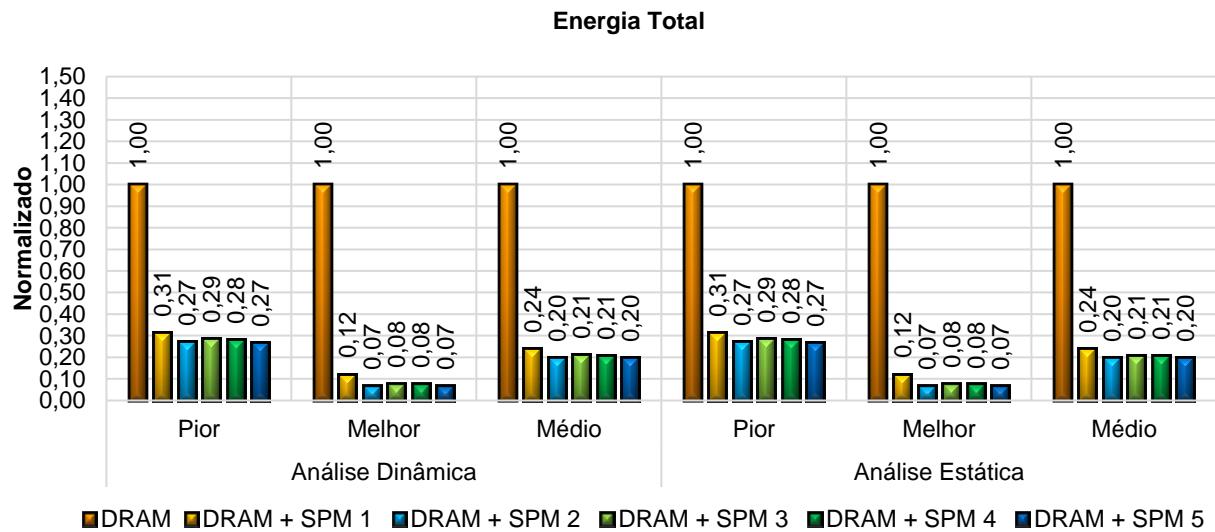

Fonte: MITTAL, VETTER e LI, 2015.