**UNIVERSIDADE FEDERAL DE PELOTAS**

**Centro de Desenvolvimento Tecnológico**

**Programa de Pós-Graduação em Computação**

Tese

**Projeto de Hardware de Alto Desempenho para Ferramentas da Predição Inter

Quadros do Codificador AV1**

**Robson André Domanski**

Pelotas, 2023

**Robson André Domanski**

**Projeto de Hardware de Alto Desempenho para Ferramentas da Predição Inter

Quadros do Codificador AV1**

Tese apresentada ao Programa de Pós-Graduação

em Computação do Centro de Desenvolvimento

Tecnológico da Universidade Federal de Pelotas,

como requisito parcial à obtenção do título de

Doutor em Ciência da Computação.

Orientador: Prof. Dr. Luciano Agostini

Coorientadores: Prof. Dr. Bruno Zatt

Prof. Dr. Marcelo Schiavon Porto

Pelotas, 2023

Universidade Federal de Pelotas / Sistema de Bibliotecas

Catalogação na Publicação

D666p Domanski, Robson Andre

Projeto de hardware de alto desempenho para

ferramentas da predição inter quadros do codificador AV1 /

Robson Andre Domanski ; Luciano Agostini, orientador ;

Bruno Zatt, Marcelo Porto, coorientadores. — Pelotas,

2023.

114 f.

Tese (Doutorado) — Programa de Pós-Graduação em

Computação, Centro de Desenvolvimento Tecnológico,

Universidade Federal de Pelotas, 2023.

1. Codec AV1. 2. Predição inter quadros. 3. Projeto de

hardware. I. Agostini, Luciano, orient. II. Zatt, Bruno,

coorient. III. Porto, Marcelo, coorient. IV. Título.

CDD : 005

**Robson André Domanski**

**Projeto de Hardware de Alto Desempenho para Ferramentas da Predição Inter

Quadros do Codificador AV1**

Tese aprovada, como requisito parcial, para obtenção do grau de Doutor em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

**Data da Defesa:** 25 de abril de 2023

**Banca Examinadora:**

Prof. Dr. Luciano Volcan Agostini (orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Daniel Palomino

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Profª. Dra. Roberta Carvalho Nobre Palau

Doutora em Ciência da Computação pela Universidade Federal de Pelotas.

Prof. Dr. Felipe Martin Sampaio

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Nuno Valentim Roma

Doutor em Engenharia Eletrotécnica e de Computadores pelo Instituto Superior

Técnico de Lisboa.

Este trabalho é dedicado às crianças adultas que,

quando pequenas, sonharam em se tornar cientistas.

## AGRADECIMENTOS

É com grande honra que expresso minha mais profunda gratidão a todos aqueles que contribuíram de forma significativa para a realização deste trabalho de pesquisa. Minha construção de conhecimento e meu trabalho durante o doutorado ocorreram de forma coletiva e colaborativa dentro do grupo de pesquisa VITECH (*Video Technology Research Group*), e desde o início me senti parte dele e fui bem recebido por todos os membros. Este trabalho representa uma contribuição importante para a área de estudo, como também uma grande importância no meu crescimento pessoal, e nada disso teria sido possível sem a colaboração de muitas pessoas.

Quero agradecer a Deus por me fazer chegar até aqui nas adversidades durante esse período. Por entrar numa área totalmente nova, pela persistência, pelo aprendizado, e por poder terminar a fase com novas experiências e conhecimentos adquiridos.

Eu gostaria de expressar minha sincera gratidão à minha família pelo apoio incondicional que me foi dado ao longo deste caminho. Sem o amor, o apoio e a paciência deles, eu não teria sido capaz de completar esta jornada. Minha família sempre me encorajou a seguir meus sonhos e a buscar o conhecimento, independentemente das dificuldades que enfrentei ao longo do caminho. A minha mãe Nair e ao meu pai Mariano (*in memoriam*), quero agradecer por me criarem com valores fortes e me motivar a buscar a excelência em tudo o que eu faço. Seus sacrifícios e dedicação incansável me inspiraram a trabalhar duro e nunca desistir, e eu sou eternamente grato por tudo o que eles fizeram por mim. Ao meu irmão Christian, quero agradecer por sua presença constante em minha vida e pelo incentivo e apoio emocional que me deu durante todo o processo de pesquisa. Por fim, quero agradecer a minha namorada Priscila, que me apoiou em todos os momentos difíceis, me dando amor e compreensão durante os anos de estudo. A todos vocês, minha família, agradeço por estarem comigo nesta jornada. Espero que este trabalho seja uma forma de retribuir o amor, a dedicação e o apoio que sempre me ofereceram.

Tenho também minha sincera gratidão ao meu orientador, Luciano Agostini, por sua orientação, paciência e encorajamento durante todo o processo de pesquisa. Sua experiência, habilidade de ensino e dedicação inabalável tornaram possível a conclusão desta tese de doutorado. Gostaria de agradecer por sua paciência e disposição em ajudar-me, principalmente ao início dessa jornada, o qual teve paciência de sentar ao meu lado e explicar e reexplicar muitas vezes algo que era totalmente novo para mim, e especialmente durante os períodos em que enfrentei dificuldades ou momentos de incerteza. E não menos importante, gostaria de agradecer a ajuda dos meus coorientadores Marcelo Porto e Bruno Zatt.

Gostaria de agradecer a todos os meus colegas de pesquisa e amigos, que estiveram ao meu lado durante todo o processo de elaboração desta tese de doutorado.

Seu apoio, conhecimento e experiência me ajudaram a crescer em minha capacidade de pesquisa e me incentivaram a persistir quando as coisas se tornaram difíceis. Primeiramente ao meu colega William, que trabalhou como bolsista desta pesquisa, que ajudou em boa parte desta jornada e o qual tive o prazer de ser coorientador do seu Trabalho de Conclusão de Curso. Aos colegas Wagner, Jones e Rafael pela troca de ideias e experiência durante toda fase do doutorado. Roberta, Ruhan, Vladimir, Alex, Murilo e Narusci gostaria de agradecer a parceira e coleguismo durante todo esse período. Por fim, gostaria de agradecer a todos os meus colegas de pesquisa, que eu tive o privilégio de conhecer e trabalhar durante o curso do meu doutorado. Sua presença e amizade tornaram esta jornada muito mais agradável e enriquecedora, e serei eternamente grato por suas contribuições neste trabalho.

Por fim, gostaria de agradecer a todos que contribuíram de alguma forma para o desenvolvimento deste trabalho.

*Lembre-se sempre, o seu foco determina a sua realidade.*

— QUI-GON JINN

## RESUMO

DOMANSKI, Robson André. **Projeto de Hardware de Alto Desempenho para Ferramentas da Predição Inter Quadros do Codificador AV1.** Orientador: Luciano Agostini. 2023. 114 f. Tese (Doutorado em Ciência da Computação) – Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2023.

Atualmente os vídeos digitais estão cada vez mais presentes no mundo inteiro, sejam eles destinados ao lazer ou as atividades profissionais. Por consequência, pode-se observar um expressivo crescimento no número de dispositivos móveis capazes de capturar, manipular e transmitir estes vídeos digitais. Esses dispositivos móveis, por sua vez, possuem sérias restrições em termos de consumo de energia e de poder computacional. Neste contexto, a codificação de vídeos é responsável por parte importante destas restrições. Os novos codificadores são desenvolvidos com o objetivo de realizar a compressão desses vídeos de forma cada vez mais eficiente e para resoluções cada vez mais elevadas, assim tornando o suporte a vídeos digitais uma operação bastante custosa do ponto de vista de poder computacional e de consumo de energia. Nesse cenário, o codificador *AOMedia Video 1* (AV1) tem ganhado destaque. O AV1 é um codificador desenvolvido por um consórcio de grandes empresas da área, como *Google*, *Apple*, *Intel*, *AMD* entre outras, com o objetivo de ter elevada eficiência de compressão em uma solução livre de royalties. Para tanto, o AV1 adotou novas ferramentas de codificação de elevado custo computacional o que amplia os desafios para que dispositivos móveis suportem esse codificador. Entre as etapas do AV1 que trouxeram maiores inovações está a predição inter quadros. Por conta destas inovações, a predição inter quadros é responsável pelo maior custo computacional no codificador AV1, com cerca de 58% do tempo de execução, principalmente quando levamos em conta que a inter quadros é uma etapa dentre as oito dentro do codificador AV1. Este trabalho apresenta um conjunto de soluções em hardware dedicado para a predição inter quadros do AV1. Foram desenvolvidas arquiteturas para Estimação de Movimento Fracionária, a Compensação de Movimento Convencional e as Compensações de Movimentos Distorcidos Local e Global. Todas as arquiteturas propostas buscaram um projeto de hardware eficiente em termos de área e potência. As arquiteturas foram sintetizadas para ASIC usando a biblioteca TSMC de 40 nm e foram capazes de processar vídeos de ultra alta definição, como UHD 4K e UHD 8K a taxas de quadros variando entre 30 e 60 quadros por segundo. As arquiteturas desenvolvidas neste trabalho são as primeiras na literatura que implementaram soluções para as ferramentas da predição inter quadros do codificador AV1.

Palavras-chave: Codec AV1. Predição Inter Quadros. Projeto de Hardware.

## ABSTRACT

DOMANSKI, Robson André. **High-Performance Hardware Design for AV1 Encoder Inter-Frame Prediction Tools.** Advisor: Luciano Agostini. 2023. 114 f. Thesis (Doctorate in Computer Science) – Technology Development Center, Federal University of Pelotas, Pelotas, 2023.

Currently, digital videos are increasingly present all over the world, whether they are intended for leisure or professional activities. Consequently, a significant growth in the number of mobile devices capable of capturing, manipulating and transmitting these digital videos can be observed. These mobile devices, in turn, have serious restrictions in terms of energy consumption and computational power. In this context, video encoding is responsible for an important part of these restrictions. New encoders are developed with the aim of compressing these videos more and more efficiently and for ever higher resolutions, thus making the support to digital videos a very costly operation from the point of view of computational power and energy consumption. In this scenario, the AOMedia Video 1 (AV1) encoder has gained prominence. AV1 is an encoder developed by a consortium of large companies in the area, such as Google, Apple, Intel, AMD, among others, with the objective of having high compression efficiency in a royalty-free solution. To this end, AV1 adopted new coding tools with a high computational cost, which increases the challenges for mobile devices to support this encoder. Among the stages of AV1 that brought greater innovations is the inter-frame prediction. Due to these innovations, the interframe prediction is responsible for the highest computational cost in the AV1 encoder, with about 58% of its the execution time, especially when we take into account that the interframe is one step among the eight within the AV1 encoder. This work presents a set of dedicated hardware solutions for AV1 inter-frame prediction. Efficient architectures were developed for Fractional Motion Estimation, Conventional Motion Compensation and Local and Global Warped Motion Compensations. All proposed architectures sought an efficient hardware design in terms of area and power. The architectures were synthesized to ASIC using the 40 nm TSMC library and they are able to process ultra high definition videos such as UHD 4K and UHD 8K at frame rates ranging between 30 and 60 frames per second. The architectures designed in this work are the first in the literature presenting solutions for the inter-frame prediction tools of the AV1 encoder.

Keywords: AV1 Codec. Inter-Frames Prediction. Hardware Design.

## LISTA DE FIGURAS

|    |                                                                                                                                                                      |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  | Linha do tempo de desenvolvimento dos principais codificadores.<br>Fonte: Adaptado de (GOEBEL, 2019). . . . .                                                        | 20 |

| 2  | Percentuais de tempo de execução dos vídeos para cada estágio de codificação para cada CQ Level do codificador AV1 (BORGES, 2020). . . . .                           | 23 |

| 3  | Diagrama de blocos genérico de codificação de vídeo. Fonte: Adaptado de (AGOSTINI; SILVA; BAMPLI, 2007). . . . .                                                     | 29 |

| 4  | Particionamento do codificador AV1. Fonte: Adaptado de (Chen et al., 2018). . . . .                                                                                  | 30 |

| 5  | Elementos presentes na Estimativa de Movimento (AFONSO; AGOSTINI; FRANCO, 2013). . . . .                                                                             | 37 |

| 6  | Exemplo de uso de múltiplos quadros de referência. . . . .                                                                                                           | 38 |

| 7  | Posição sub-pixel FME. . . . .                                                                                                                                       | 42 |

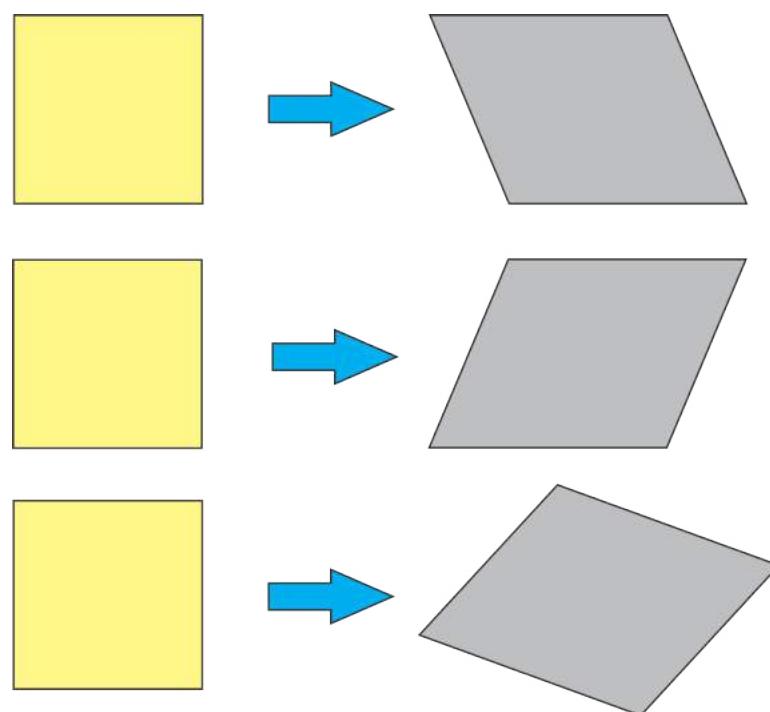

| 8  | Exemplos de transformações afins. Adaptado de (KOLODZIEJSKI; DOMANSKI; AGOSTINI, 2022). . . . .                                                                      | 45 |

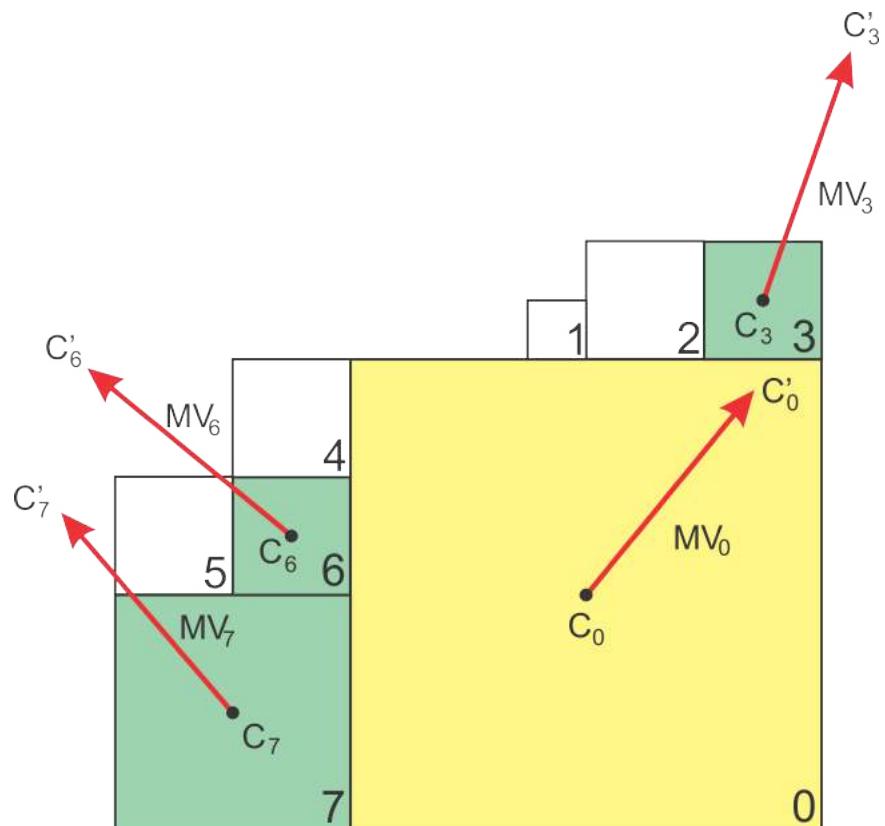

| 9  | Bloco atual em amarelo. Os blocos vizinhos que se referem à mesma imagem de referência que o bloco atual estão em verde. Adaptado de (Parker et al., 2017a). . . . . | 46 |

| 10 | Cisalhamento horizontal, vertical e combinado, respectivamente. Adaptado de (OPEN MEDIA, 2022). . . . .                                                              | 48 |

| 11 | Fluxograma da Compensação de Movimento Distorcido Global. . . . .                                                                                                    | 52 |

| 12 | Arquitetura de interpolação multi-filtro (MFIA) para a Compensação de Movimento do AV1. . . . .                                                                      | 62 |

| 13 | Arquitetura do interpolador usado na MC do AV1 denominado 1RC. . . . .                                                                                               | 64 |

| 14 | Arquitetura do interpolador usado na MC do AV1 denominado 2RC. . . . .                                                                                               | 65 |

| 15 | Arquitetura do interpolador usado na MC do AV1 denominado 4RC. . . . .                                                                                               | 66 |

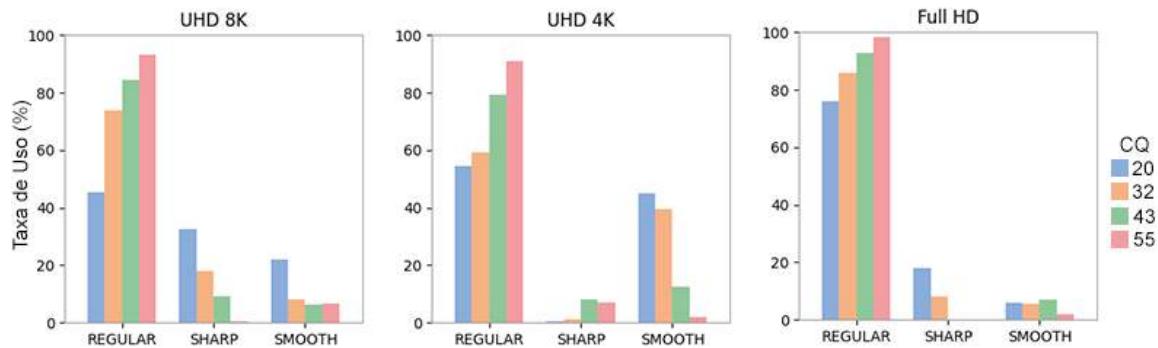

| 16 | Percentuais de vezes que cada filtro é usado na FME do AV1. . . . .                                                                                                  | 70 |

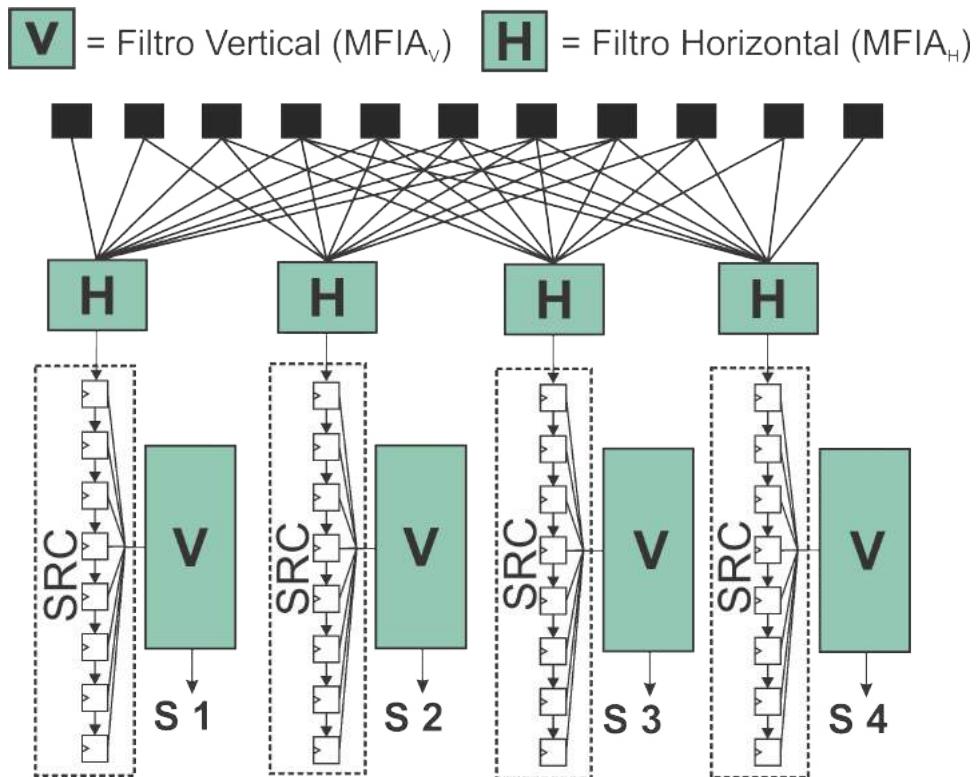

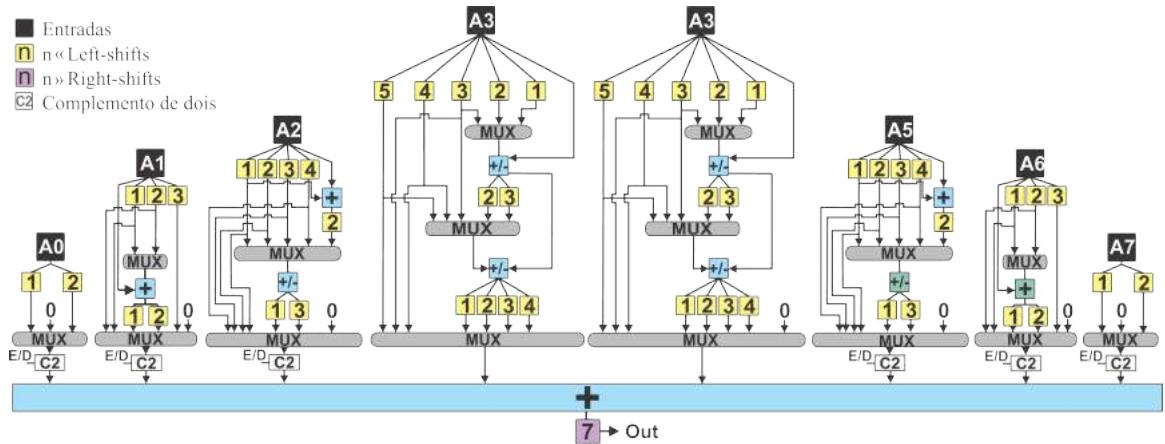

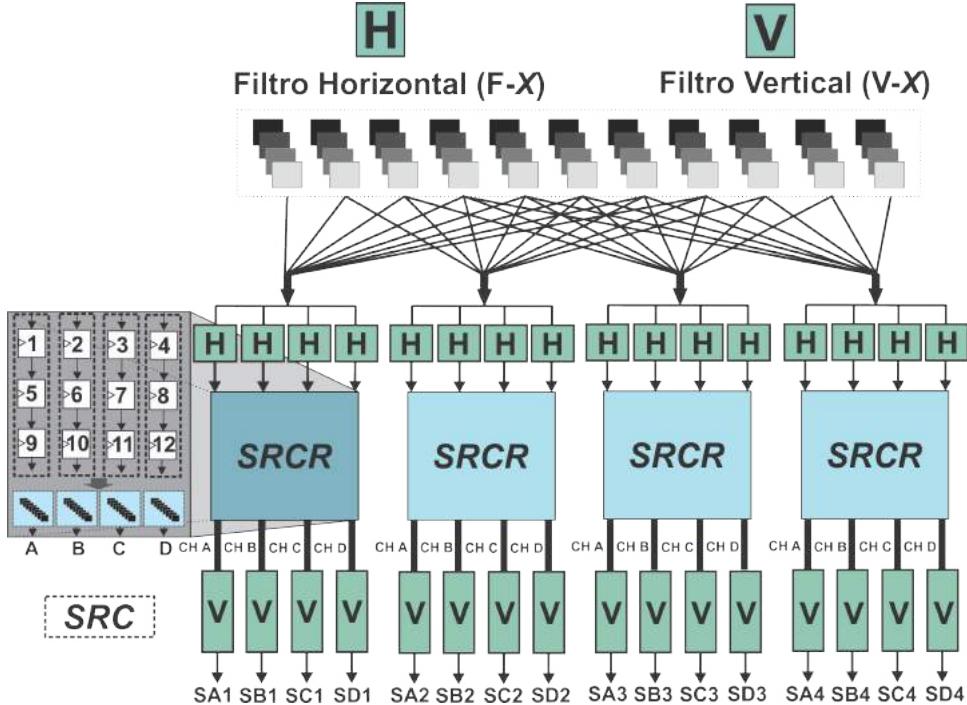

| 17 | Arquitetura multi-filtro original (OM) usada na FME do AV1. . . . .                                                                                                  | 71 |

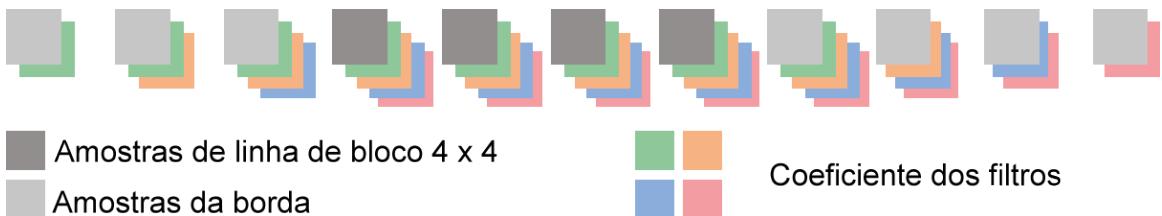

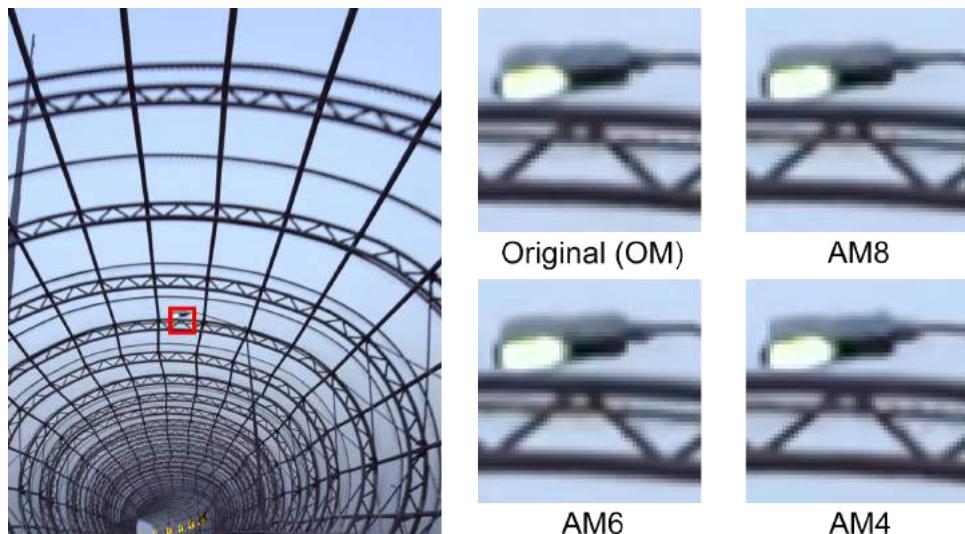

| 18 | Exemplo de amostras usadas na interpolação. . . . .                                                                                                                  | 74 |

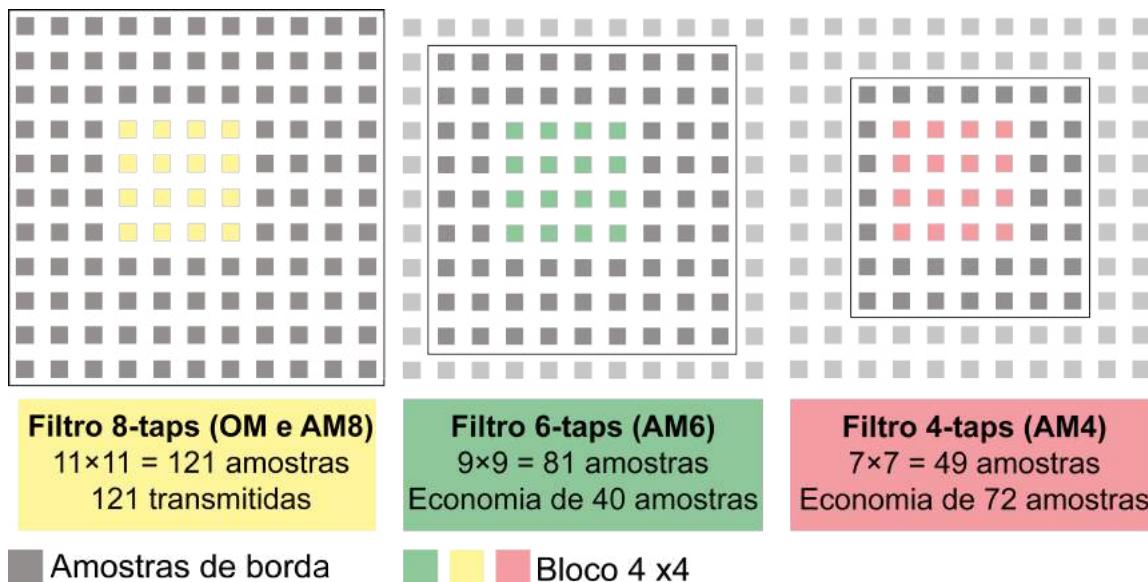

| 19 | Amostras necessárias para interpolar um bloco $4 \times 4$ usando filtros de 8, 6 e 4 taps. . . . .                                                                  | 75 |

| 20 | Comparação de qualidade visual extraída de uma sequência manipulada nos testes. . . . .                                                                              | 77 |

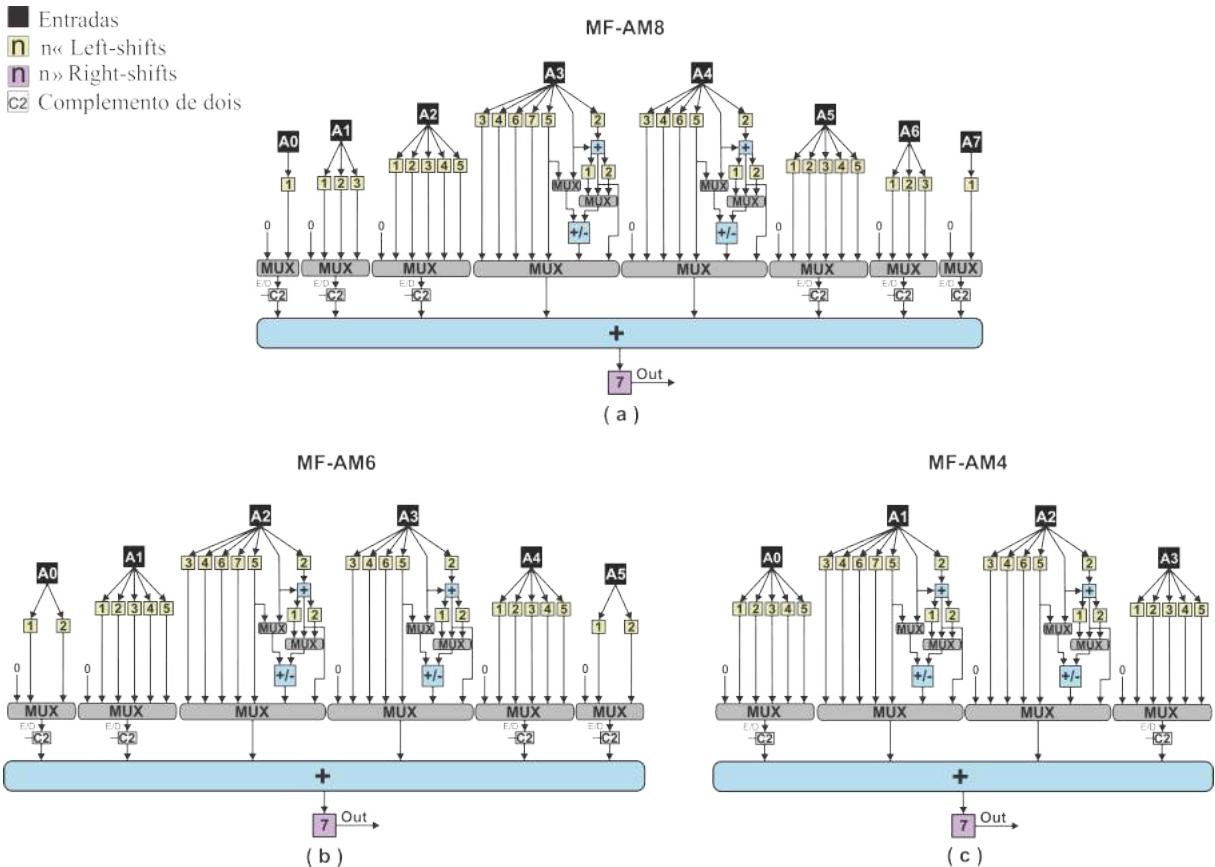

| 21 | Arquiteturas de interpolação multi-filtro da FME do AV1 usando a solução AM8 (MF-AM8), AM6 (MF-AM6) e AM4 (MF-AM4). . . . .                                          | 79 |

|    |                                                                                                                                                                                            |     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

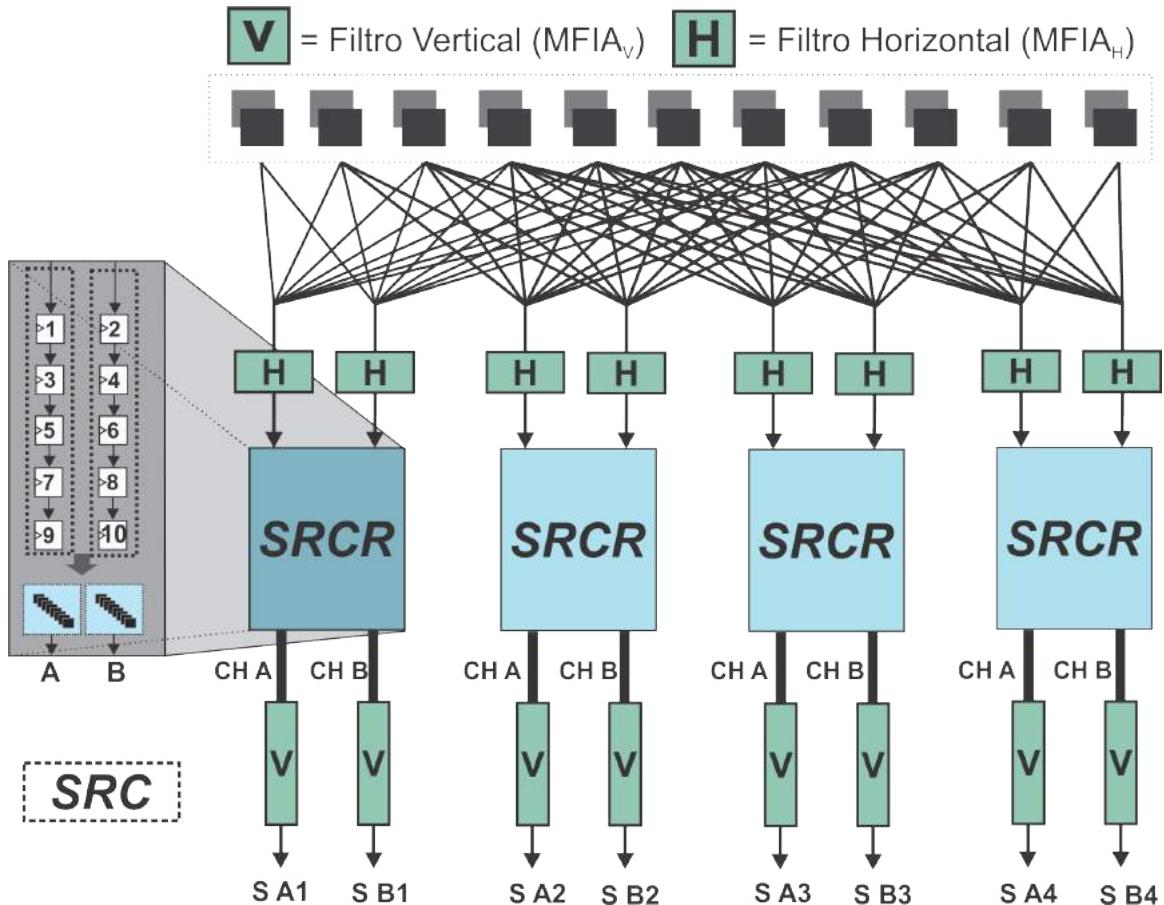

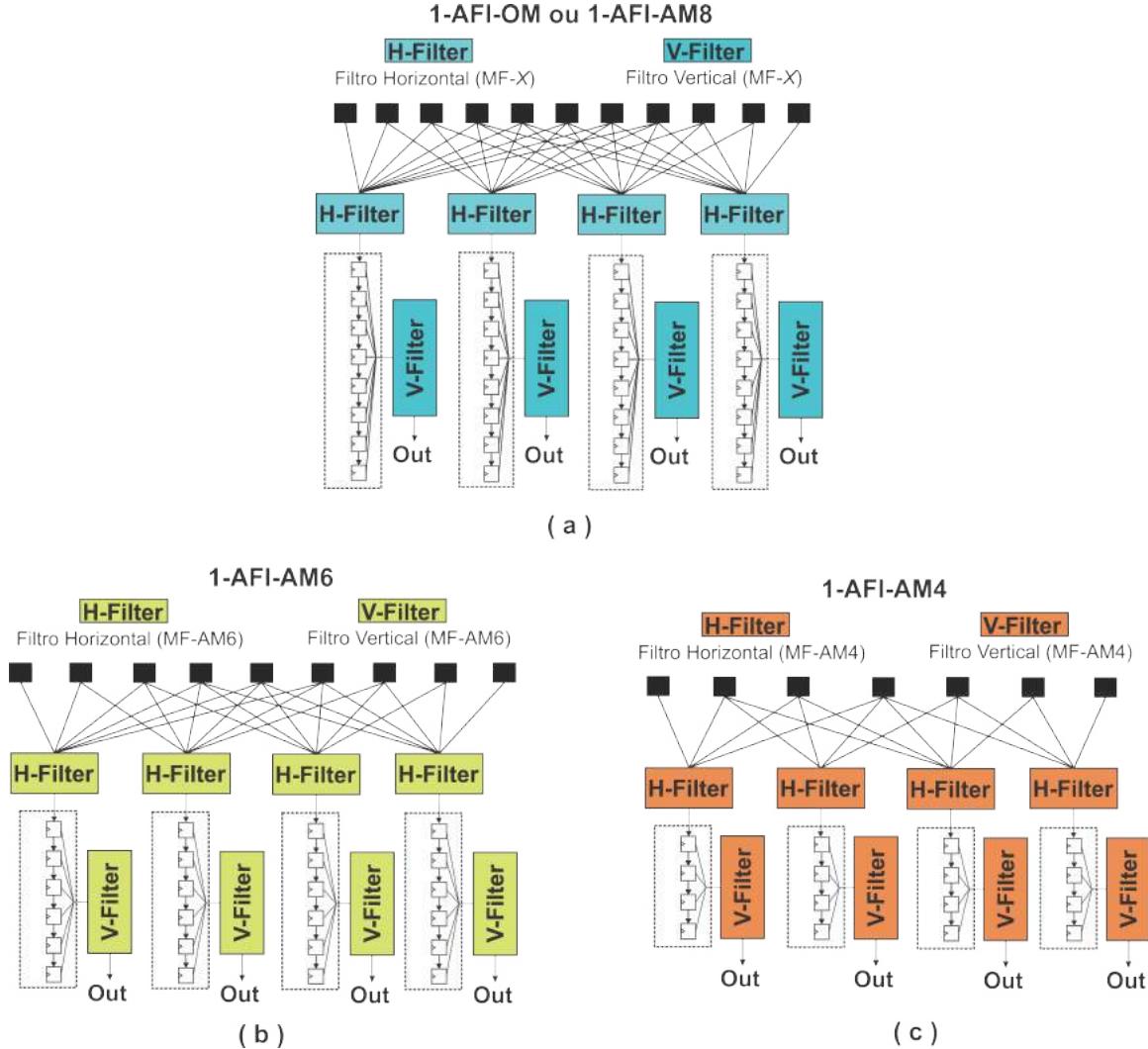

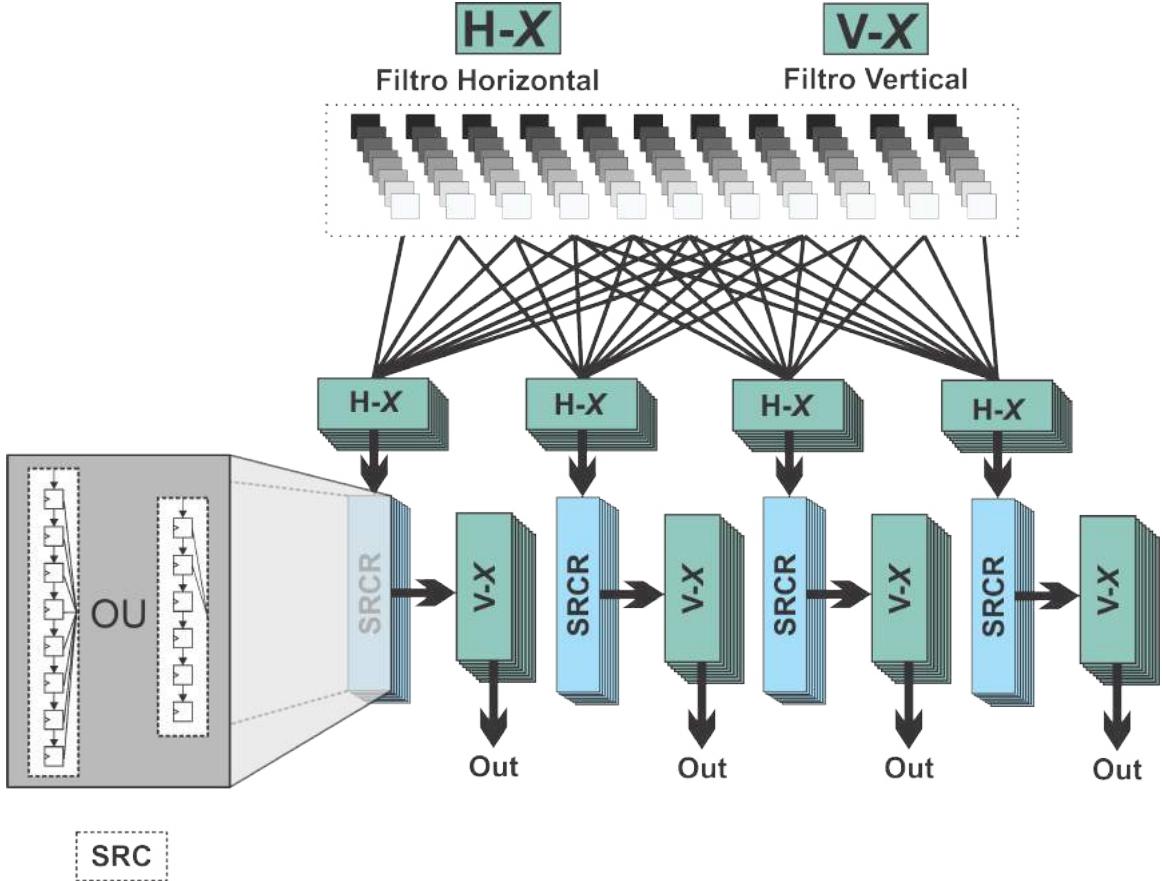

| 22 | Arquiteturas dos interpoladores da FME do AV1 usando uma instâncias de MF-OM ou MF-AM8 (1-AFI-OM ou 1-AFI-AM8), MF-AM6 (1-AFI-AM6) e MF-AM4 (1-AFI-AM4). . . . .                           | 81  |

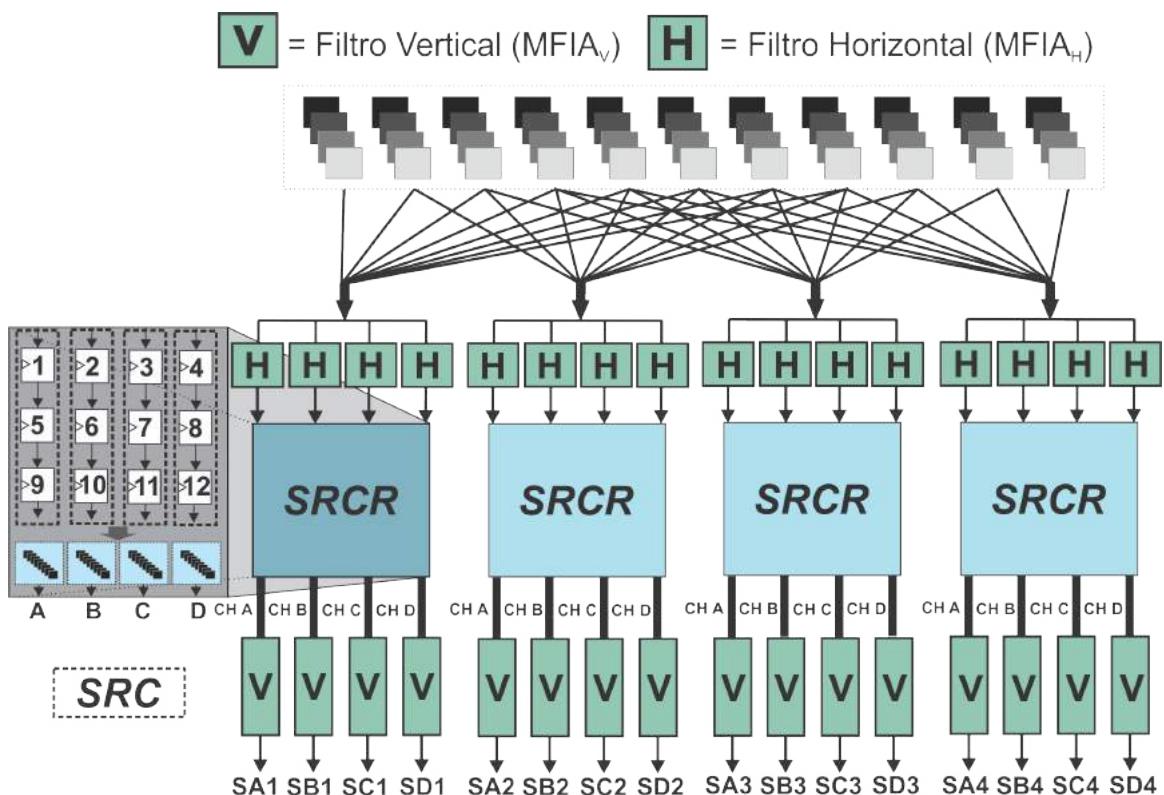

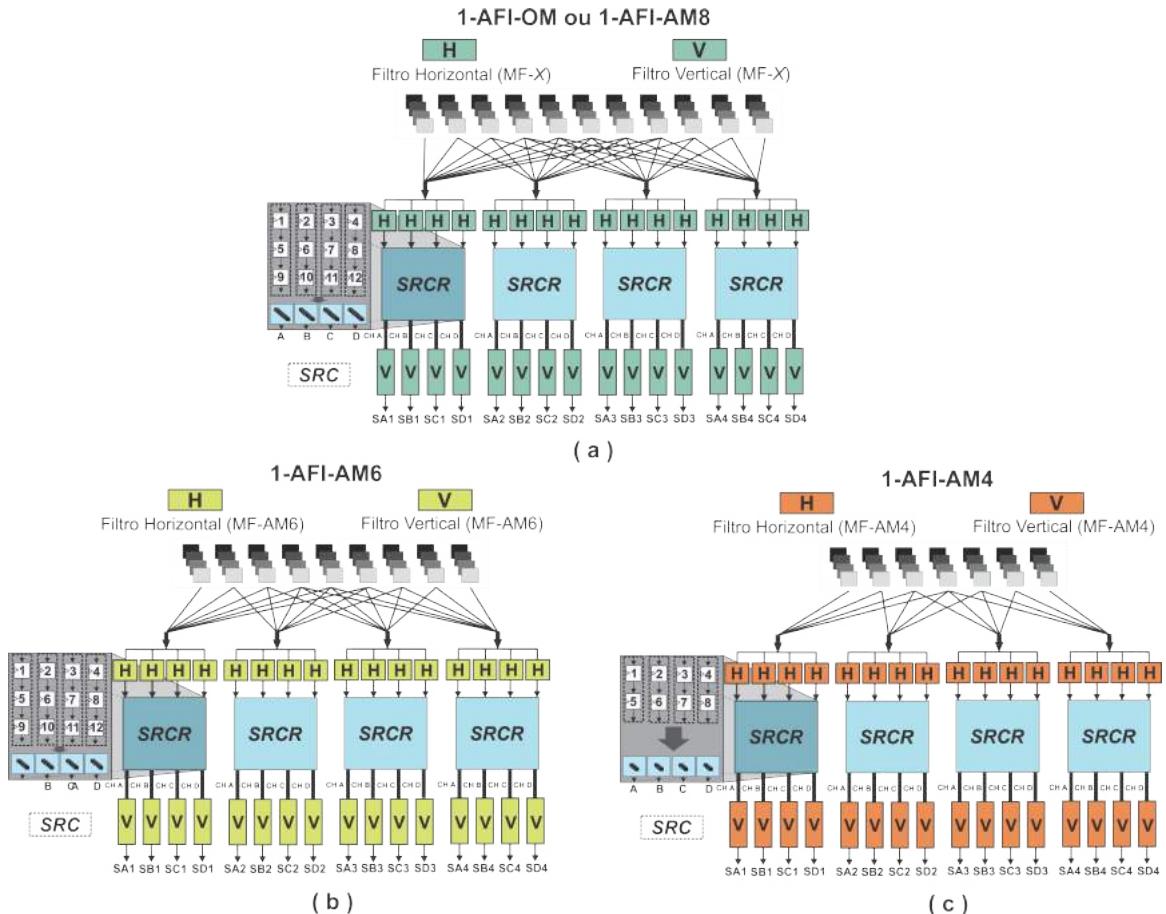

| 23 | Arquiteturas dos interpoladores da FME do AV1 usando quatro instâncias de MF-OM ou MF-AM8 (4-AFI-OM ou 4-AFI-AM8), MF-AM6 (4-AFI-AM6) e MF-AM4 (4-AFI-AM4). . . . .                        | 82  |

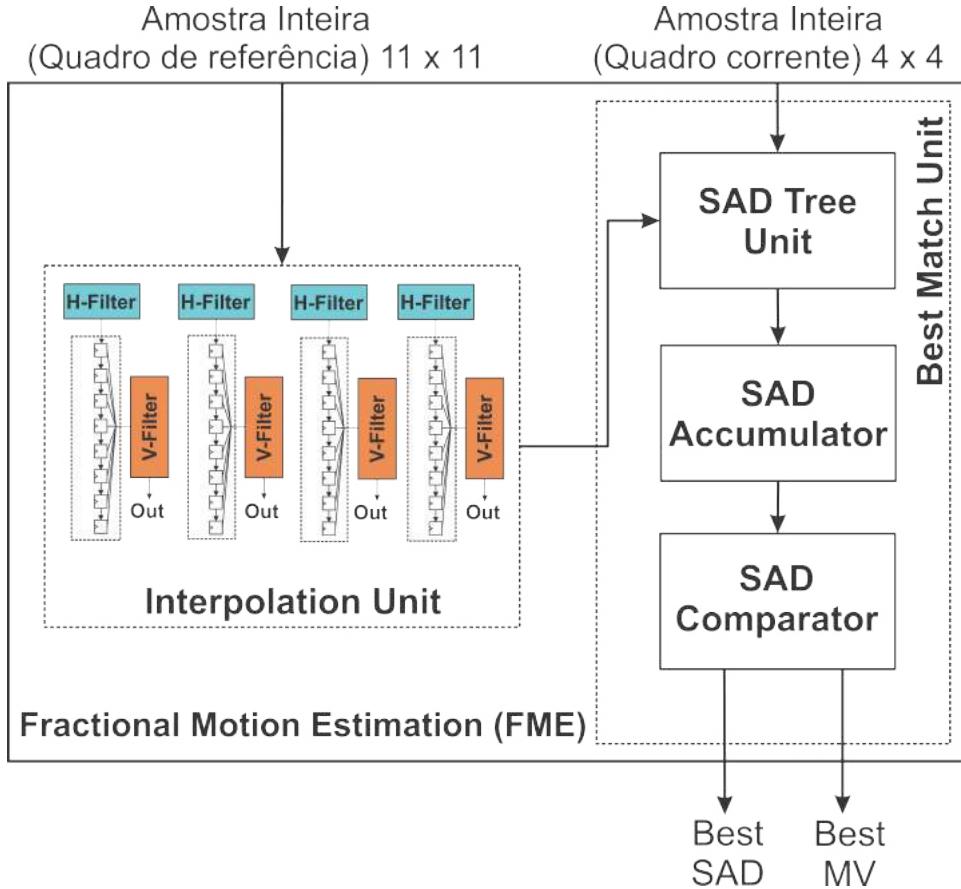

| 24 | Diagrama da arquitetura completa da FME usada no codificador AV1. . . . .                                                                                                                  | 85  |

| 25 | Arquitetura do interpolador usado no bloco UI com quatro instâncias dos multi-filtros projetados denominada 4-AF-X. . . . .                                                                | 87  |

| 26 | Arquitetura do interpolador usado no bloco UI com oito instâncias dos multi-filtros projetados denominada 8-AF-X. . . . .                                                                  | 88  |

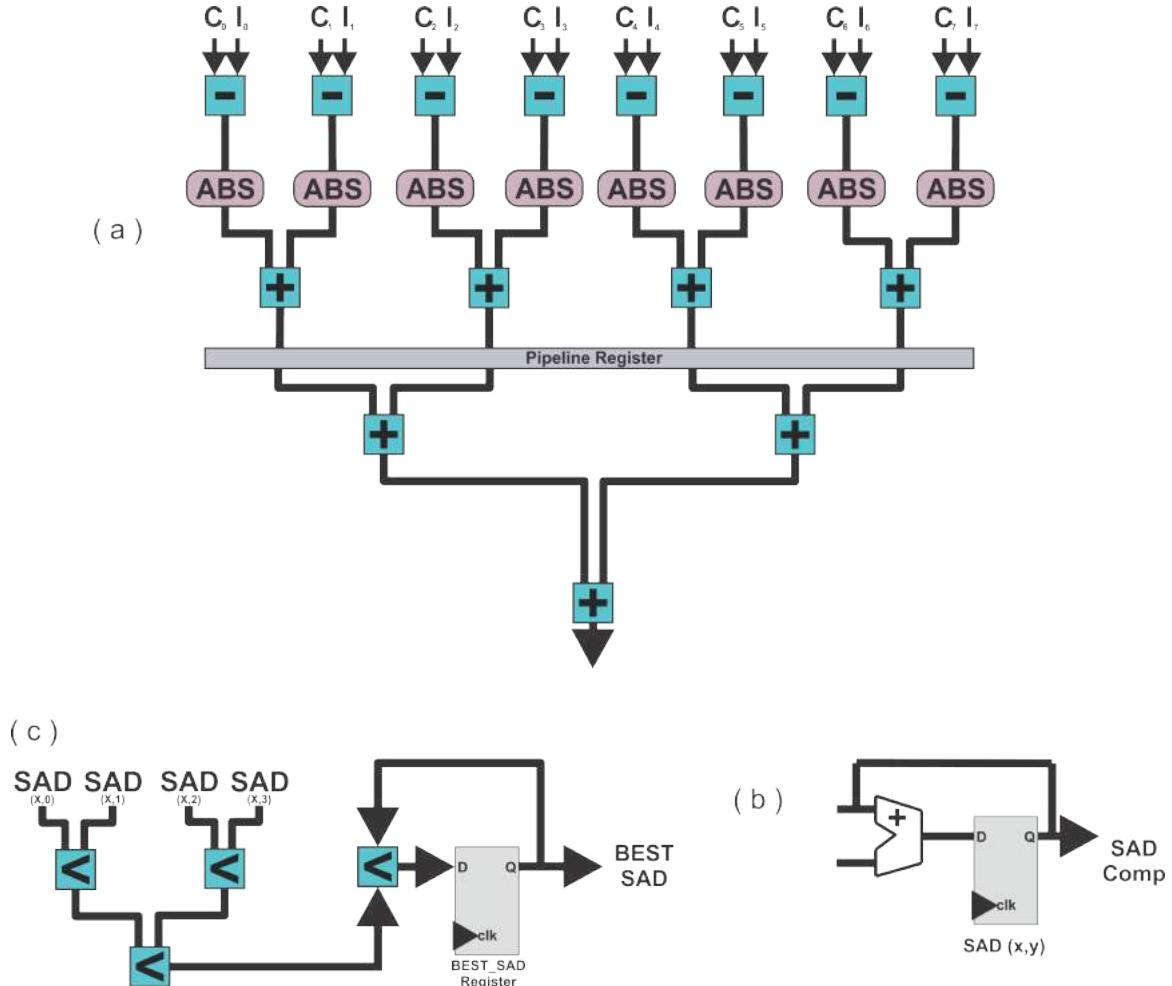

| 27 | Arquitetura da etapa de Unidade de Melhor Casamento da FME do AV1: (a) Arquitetura Unidade de Árvore de SAD ; (b) Arquitetura Acumulador de SAD (c) Arquitetura Comparador de SAD. . . . . | 89  |

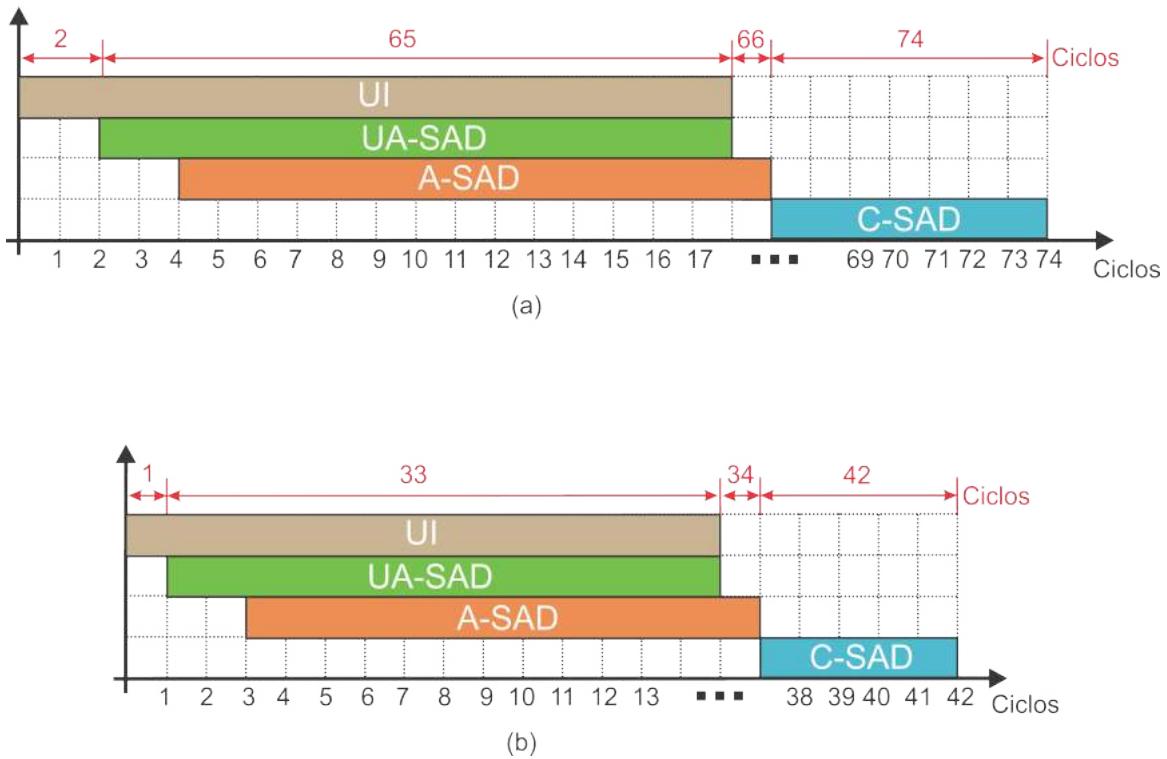

| 28 | Diagrama temporal da FME do AV1: (a) Processamento da arquitetura 4-AF-X; (b) Processamento da arquitetura 8-AF-X. . . . .                                                                 | 90  |

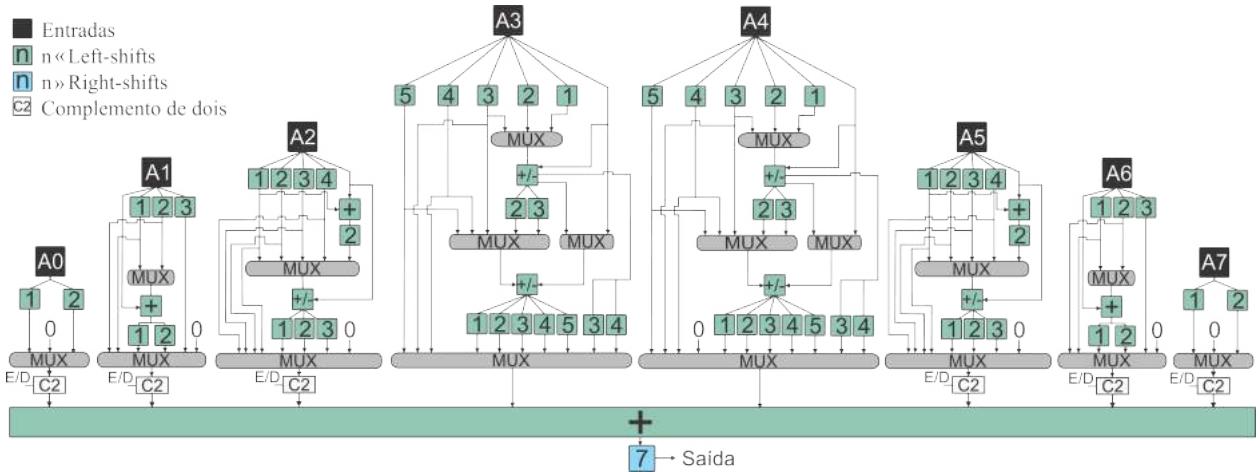

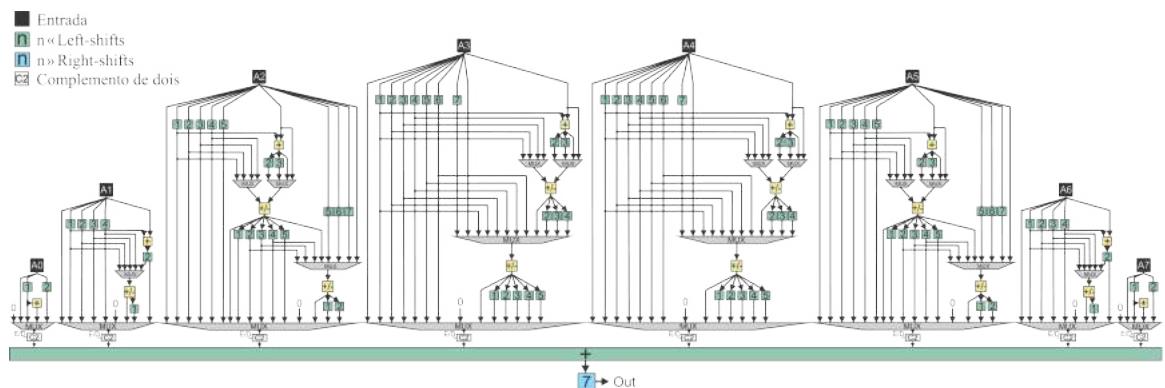

| 29 | Arquitetura multi-filtro para a Compensação de Movimento Distorcido Local (AMDL). . . . .                                                                                                  | 93  |

| 30 | Arquitetura do Interpolador para Compensação do Movimento Distorcido Local com Uma Linha por Ciclo (1L-AIDL). . . . .                                                                      | 95  |

| 31 | Arquitetura do Interpolador para Compensação de Movimento Distorcido Local com Quatro Linhas por Ciclo (4L-AIDL) . . . . .                                                                 | 96  |

| 32 | Fluxograma da arquitetura da compensação de movimento distorcido global. . . . .                                                                                                           | 98  |

| 33 | Círculo de Bresenham utilizado no algoritmo FAST. Adaptado de (ROSTEN; DRUMMOND, 2006). . . . .                                                                                            | 99  |

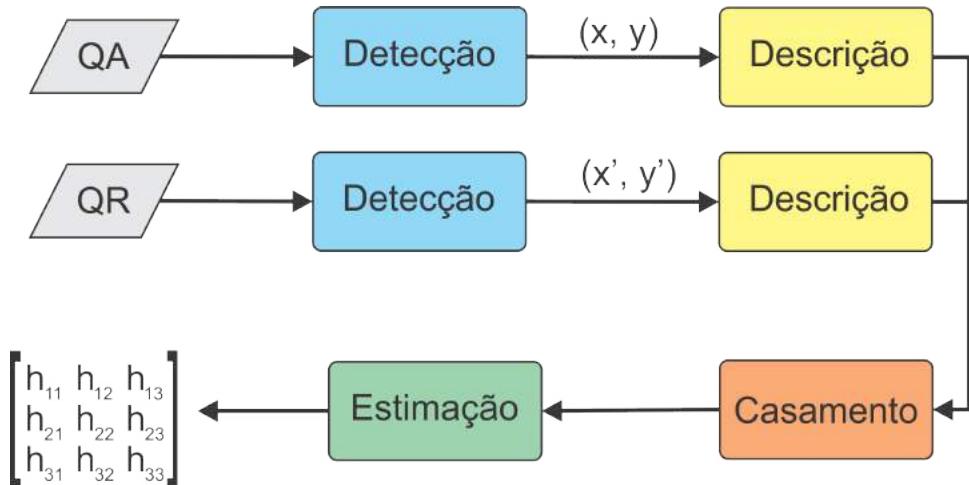

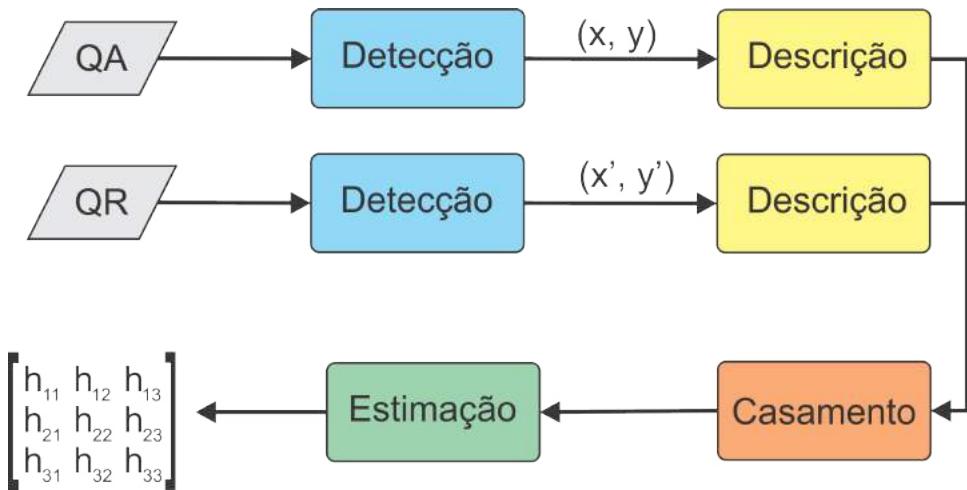

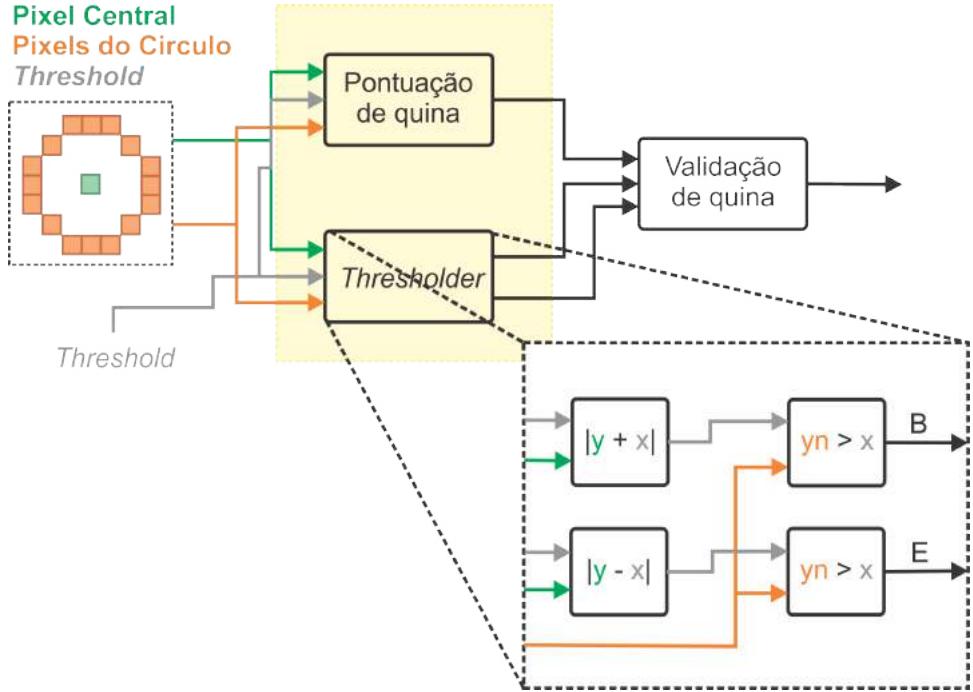

| 34 | Arquitetura da etapa de Detecção usada na GWMC. . . . .                                                                                                                                    | 100 |

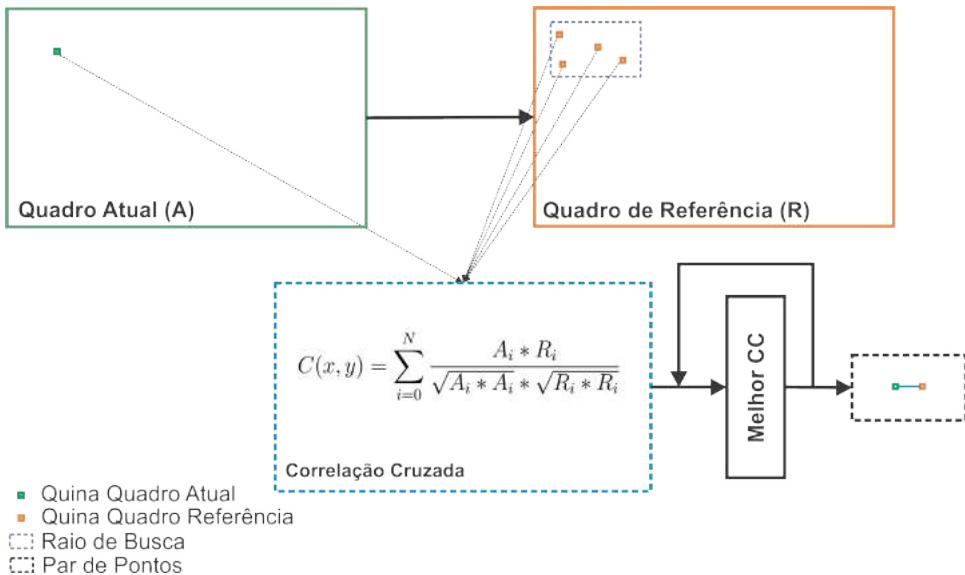

| 35 | Arquitetura da etapa de Descrição e Casamento usada na GWMC. . . . .                                                                                                                       | 101 |

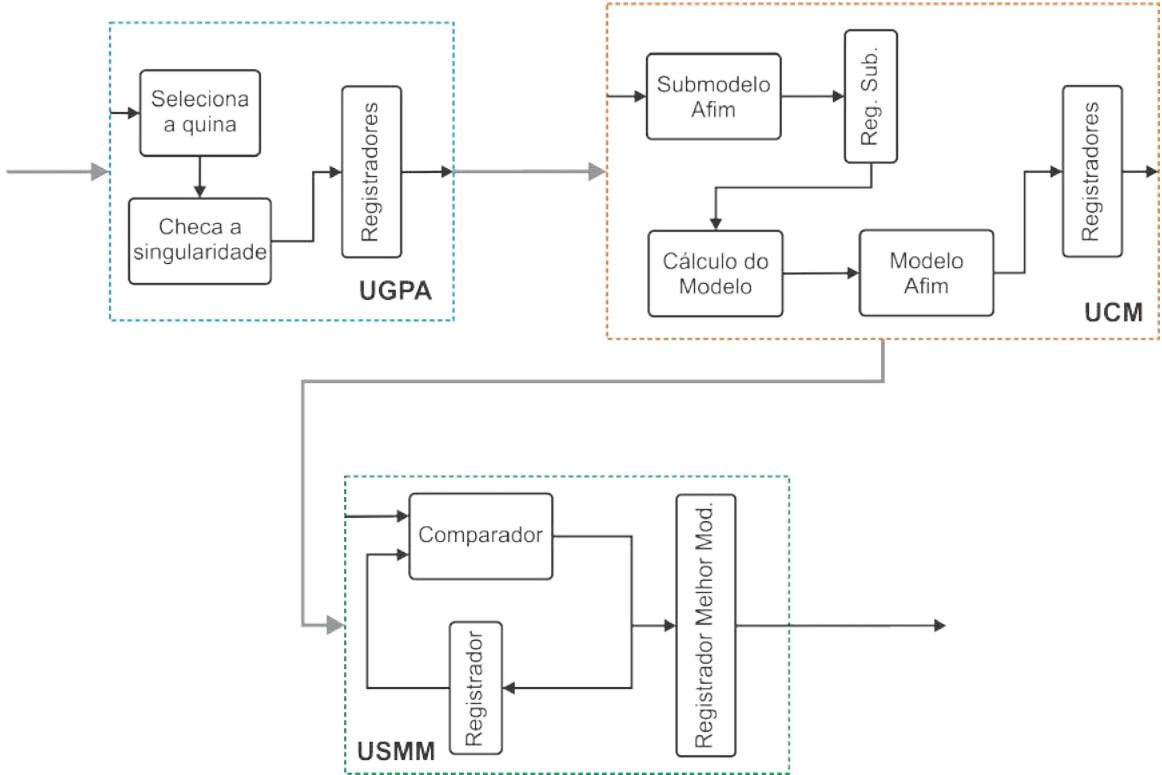

| 36 | Arquitetura de Hardware da etapa de Estimação usada na GWMC. . . . .                                                                                                                       | 102 |

## **LISTA DE TABELAS**

|    |                                                                                           |     |

|----|-------------------------------------------------------------------------------------------|-----|

| 1  | Coeficientes dos filtros: Regular 6 taps, Smooth 6 taps e Sharp 8 taps                    | 40  |

| 2  | Coeficientes dos filtros: Regular 4 taps, Smooth 4 taps e Bilinear 2 taps                 | 41  |

| 3  | Filtros FIR da Compensação de Movimento Distorcido Local . . . . .                        | 49  |

| 4  | Sumário comparativo da predição inter quadros dos codificadores HEVC e AV1 . . . . .      | 58  |

| 5  | Resultados de sínteses para as arquiteturas usadas na MC do AV1.                          | 67  |

| 6  | Coeficientes originais e modificados dos filtros do AV1. . . . .                          | 73  |

| 7  | Amostras Necessárias por Tamanho de Bloco . . . . .                                       | 75  |

| 8  | Resultado Eficiência de Codificação . . . . .                                             | 76  |

| 9  | Uso de hardware nas três arquiteturas multi-filtro usadas na FME do AV1 . . . . .         | 79  |

| 10 | Resultados de sínteses para as arquiteturas multi-filtro da FME do AV1 . . . . .          | 80  |

| 11 | Resultados de sínteses para as arquiteturas do interpolador usado na FME do AV1 . . . . . | 84  |

| 12 | Resultados de sínteses para as arquiteturas completa da FME do AV1                        | 90  |

| 13 | Resultados de síntese das arquiteturas projetadas para a LWMC do AV1. . . . .             | 97  |

| 14 | Resultados de síntese das arquiteturas projetadas para a GWMC do AV1. . . . .             | 103 |

## LISTA DE ABREVIATURAS E SIGLAS

|         |                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------|

| 1L-AIDL | Arquitetura do Interpolador para Compensação do Movimento Distorcido Local com Uma Linha por Ciclo     |

| 4L-AIDL | Arquitetura do Interpolador para Compensação de Movimento Distorcido Local com Quatro Linhas por Ciclo |

| A-SAD   | Acumulador de SAD                                                                                      |

| AVC     | Advanced Video Coding                                                                                  |

| AOMedia | Alliance for Open Media                                                                                |

| AV1     | AOMedia Video 1                                                                                        |

| AM4     | Approximate Multiplierless with 4-taps                                                                 |

| AM6     | Approximate Multiplierless with 6-taps                                                                 |

| AM8     | Approximate Multiplierless with 8-taps                                                                 |

| AMDL    | Arquitetura Multifiltro para a Compensação de Movimento Distorcido Local                               |

| MFIA    | Arquitetura de Interpolação Multifiltro                                                                |

| ADST    | Asymmetric Discrete Sine Transform                                                                     |

| AFI-AM4 | AV1 FME Interpolation using AM4                                                                        |

| AFI-AM6 | AV1 FME Interpolation using AM6                                                                        |

| AFI-AM8 | AV1 FME Interpolation using AM8                                                                        |

| AFI-OM  | AV1 FME Interpolation using OM                                                                         |

| BD-BR   | Bjøntegaard Delta Bit Rate                                                                             |

| BD-PSNR | Bjøntegaard Delta PSNR                                                                                 |

| HS      | Cisalhamento Horizontal                                                                                |

| VS      | Cisalhamento Vertical                                                                                  |

| VCTQM   | Codec de Vídeo e Medição de Qualidade                                                                  |

| C-SAD   | Comparador de SAD                                                                                      |

| CDEF    | Constrained Directional Enhancement Filter                                                             |

| CQ      | Constrained Quality                                                                                    |

| CDF     | Cumulative Distribution Function                                                                       |

|            |                                                               |

|------------|---------------------------------------------------------------|

| DBF        | Deblocking Filter                                             |

| dB         | Decibéis                                                      |

| DCT        | Discrete Cosine Transform                                     |

| FAST       | Features from Accelerated Segment Test                        |

| FIR        | Finite Impulse Response                                       |

| FIR        | Finite Impulse Response                                       |

| FlipADST   | Flipped Asymmetric Discrete Sine Transform                    |

| FME        | Fracional Motion Estimation                                   |

| FPS        | Frames per Second                                             |

| GPP        | General Purpose Processor                                     |

| GWMC       | Global Warped Motion Compensation                             |

| GPU        | Graphic Processing Unit                                       |

| HEVC       | High Efficiency Vido Coding                                   |

| HVS        | Human Visual System                                           |

| IDTX       | Identity Transform                                            |

| ISCAS      | IEEE International Symposium on Circuits and Systems          |

| LASCAS     | IEEE Latin American Symposium on Circuits and Systems         |

| IME        | Integer Motion Estimation                                     |

| ISO        | International Organization for Standarlization                |

| ITU-T      | International Telecommunications Union                        |

| IDL        | Interpolador para a Compensação de Movimento Distorcido Local |

| Intra - BC | Intra Block Copy                                              |

| JVET       | Joint Video Experts Team                                      |

| LWMC       | Local Warped Motion Compensation                              |

| LFNSST     | Low Frequency Non-Separable Secondary Transform               |

| MC         | Motion Compensation                                           |

| ME         | Motion Estimation                                             |

| MV         | Motion Vector                                                 |

| MF-AM4     | Multifilter AM4                                               |

| MF-AM6     | Multifilter AM6                                               |

| MF-AM8     | Multifilter AM8                                               |

| MF-OM      | Multifilter OM                                                |

| MCM        | Multiple Constant Multiplication                              |

| OM         | Original Multifilter                                          |

|         |                                         |

|---------|-----------------------------------------|

| OBMC    | Overlapped Block Motion Compensation    |

| PSNR    | Peak Signal-to-Noise Ratio              |

| RANSAC  | Random Sample Consensus                 |

| SRC     | Shift Register Chains                   |

| SRCR    | Shift-Register Chain Router             |

| SRC     | Shift-Register-Chain                    |

| SAD     | Sum of Absolute Differences             |

| SB      | SuperBlocks                             |

| SLRF    | Switchable Loop Restoration Filter      |

| TCAS-II | Transactions on Circuits and Systems II |

| UA-SAD  | Unidade de Árvore de SAD                |

| UCM     | Unidade de Cálculo do Modelo            |

| UHD     | Ultra High Definition                   |

| UI      | Unidade de Interpolação                 |

| UMC     | Unidade de Melhor Casamento             |

| USMM    | Unidade de Seleção do Melhor Modelo     |

| UGPA    | Unidade Geradora de Pontos Aleatórios   |

| VVC     | Versatile Video Coding                  |

| VCEG    | Video Coding Experts Group              |

| VITECH  | Video Technology Research Group         |

| WMC     | Warped Motion Compensation              |

# SUMÁRIO

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

| <b>1 INTRODUÇÃO . . . . .</b>                                                                 | 19 |

| 1.1 Questão e Hipótese de Pesquisa . . . . .                                                  | 24 |

| 1.2 Objetivos e Contribuições . . . . .                                                       | 25 |

| 1.3 Apresentação do Texto . . . . .                                                           | 26 |

| <b>2 CONCEITOS DE COMPRESSÃO DE VÍDEOS E O FORMATO AV1 . . . . .</b>                          | 27 |

| <b>2.1 Codificador de Video AV1 . . . . .</b>                                                 | 29 |

| 2.1.1 Partição de Blocos . . . . .                                                            | 30 |

| 2.1.2 Predição Intra Quadro . . . . .                                                         | 31 |

| 2.1.3 Predição Inter Quadros . . . . .                                                        | 32 |

| 2.1.4 Transformadas e Quantização . . . . .                                                   | 33 |

| 2.1.5 Codificação de Entropia . . . . .                                                       | 33 |

| 2.1.6 Filtragem de Laço . . . . .                                                             | 34 |

| <b>2.2 Métricas de Avaliação . . . . .</b>                                                    | 34 |

| <b>3 FERRAMENTAS DA PREDIÇÃO INTER QUADROS DO CODIFICADOR AV1</b> . . . . .                   | 36 |

| <b>3.1 Estimação de Movimento . . . . .</b>                                                   | 36 |

| 3.1.1 Estimação de Movimento Inteira . . . . .                                                | 37 |

| 3.1.2 Estimação de Movimento Fracionária . . . . .                                            | 38 |

| <b>3.2 Compensação de Movimento Convencional . . . . .</b>                                    | 41 |

| <b>3.3 Compensação de Movimento Distorcido . . . . .</b>                                      | 42 |

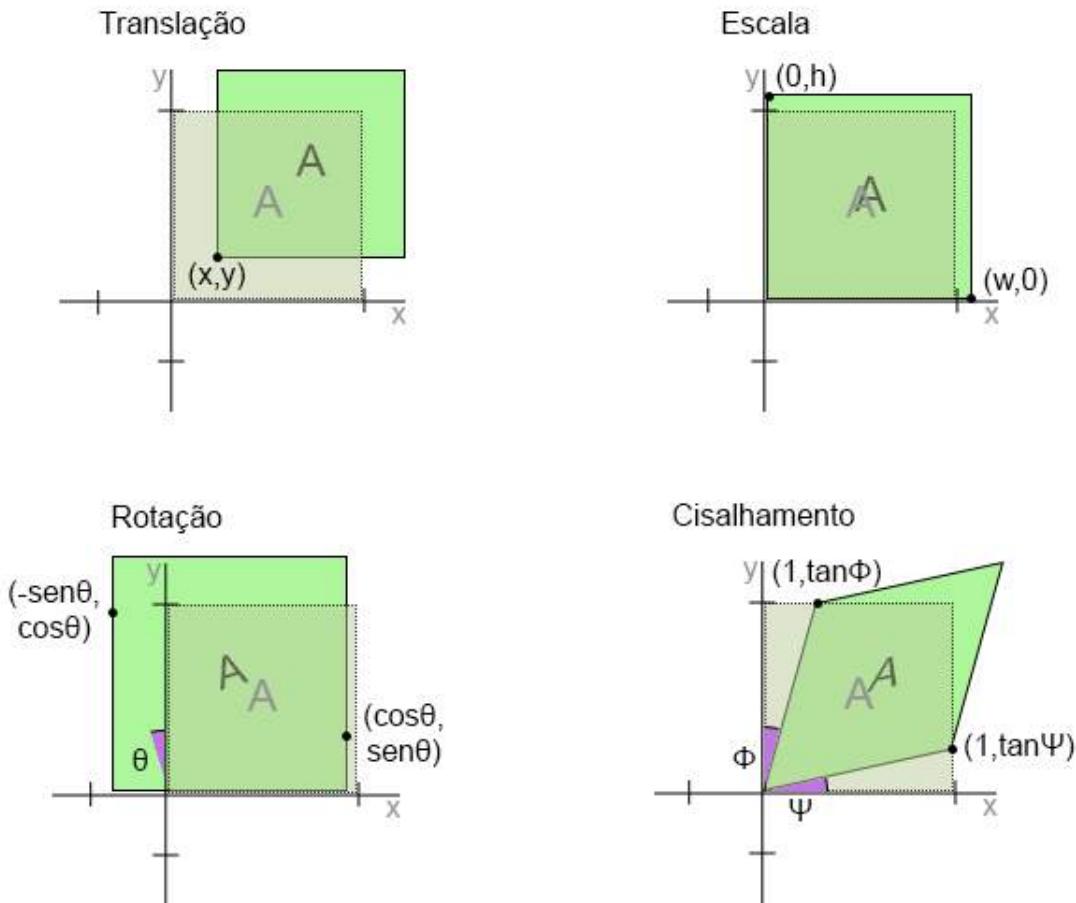

| 3.3.1 Transformações Afins . . . . .                                                          | 43 |

| 3.3.2 Compensação de Movimento Distorcido Local . . . . .                                     | 44 |

| 3.3.3 Compensação de Movimento Distorcido Global . . . . .                                    | 48 |

| <b>4 TRABALHOS RELACIONADOS . . . . .</b>                                                     | 55 |

| <b>4.1 Trabalhos com Foco na Predição Inter Quadros do AV1 . . . . .</b>                      | 55 |

| <b>4.2 Trabalhos com Foco na Predição Inter Quadros do HEVC . . . . .</b>                     | 56 |

| <b>4.3 Trabalhos com Computação Aproximada com Foco na Predição Inter Quadros . . . . .</b>   | 57 |

| <b>4.4 Conclusão Capítulo . . . . .</b>                                                       | 57 |

| <b>5 ARQUITETURA PARA O INTERPOLADOR DE SUBAMOSTRAS DA COMPENSAÇÃO DE MOVIMENTO . . . . .</b> | 60 |

| <b>5.1 Metodologia . . . . .</b>                                                              | 60 |

| <b>5.2 Filtro Usado na Interpolação da MC do AV1 . . . . .</b>                                | 61 |

| <b>5.3 Interpolador Usado na MC do AV1 . . . . .</b>                                          | 63 |

| <b>5.4 Análise e Resultados . . . . .</b>                                                     | 67 |

|                                                                                                |     |

|------------------------------------------------------------------------------------------------|-----|

| <b>6 ARQUITETURAS DESENVOLVIDAS PARA A ESTIMAÇÃO DE MOVIMENTO FRACIONÁRIA DO AV1</b> . . . . . | 69  |

| <b>6.1 Arquitetura dos Filtros</b> . . . . .                                                   | 69  |

| <b>6.2 Arquiteturas do Interpolador</b> . . . . .                                              | 80  |

| <b>6.3 Arquitetura da FME Completa</b> . . . . .                                               | 84  |

| <b>6.3.1 Unidade de Interpolação</b> . . . . .                                                 | 86  |

| <b>6.3.2 Unidade de Melhor Casamento</b> . . . . .                                             | 86  |

| <b>6.3.3 Análise e Resultados</b> . . . . .                                                    | 88  |

| <b>7 ARQUITETURAS PARA A COMPENSAÇÃO DE MOVIMENTO DISTORCIDO</b> 92                            | 92  |

| <b>7.1 Arquitetura para a Compensação de Movimento Distorcido Local</b> . . . . .              | 92  |

| <b>7.1.1 Arquitetura Multifiltro para a Compensação de Movimento Distorcido Local</b> 93       | 93  |

| <b>7.1.2 Interpolador para a Compensação de Movimento Distorcido Local</b> . . . . .           | 94  |

| <b>7.1.3 Análise e Resultados</b> . . . . .                                                    | 97  |

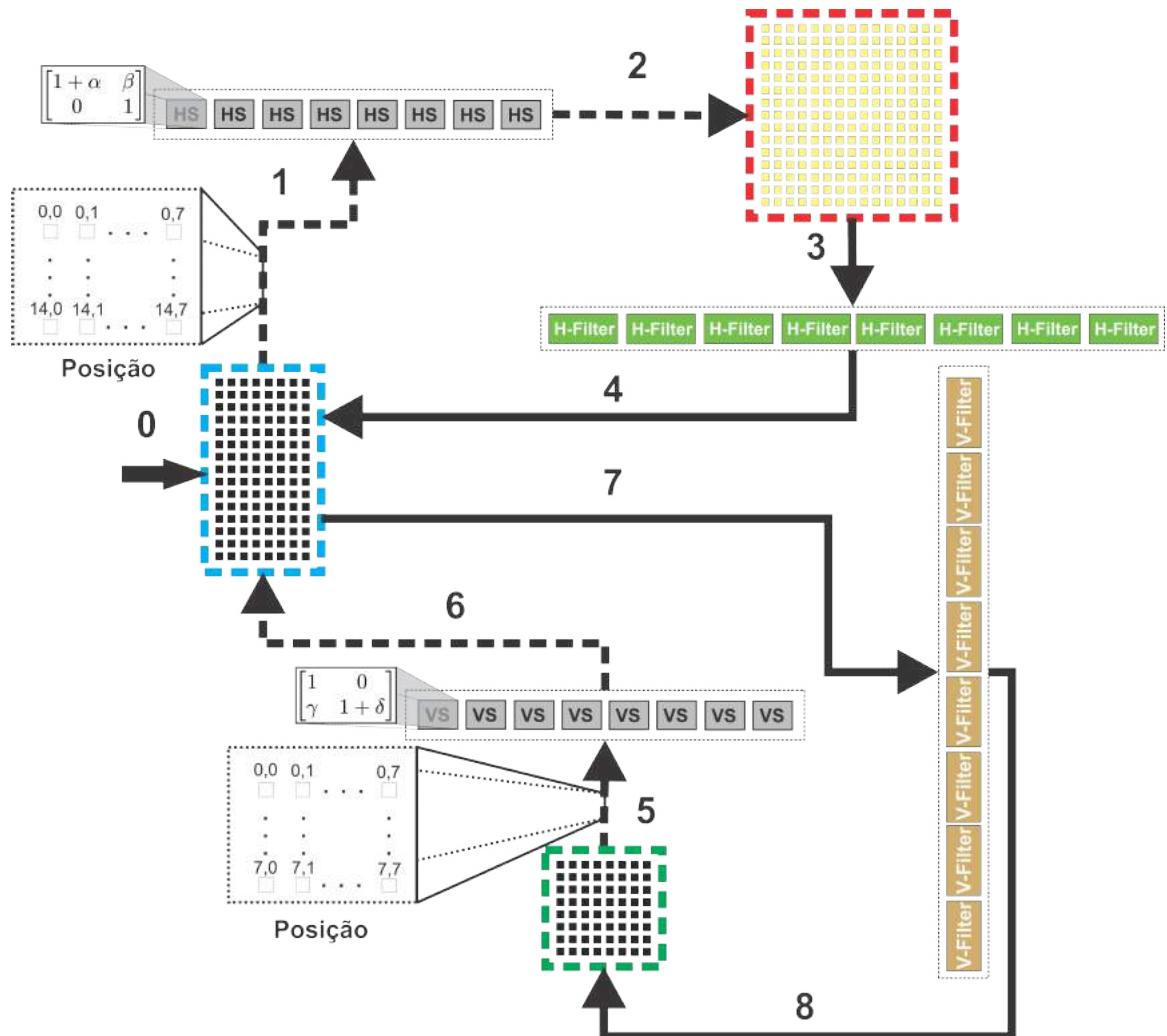

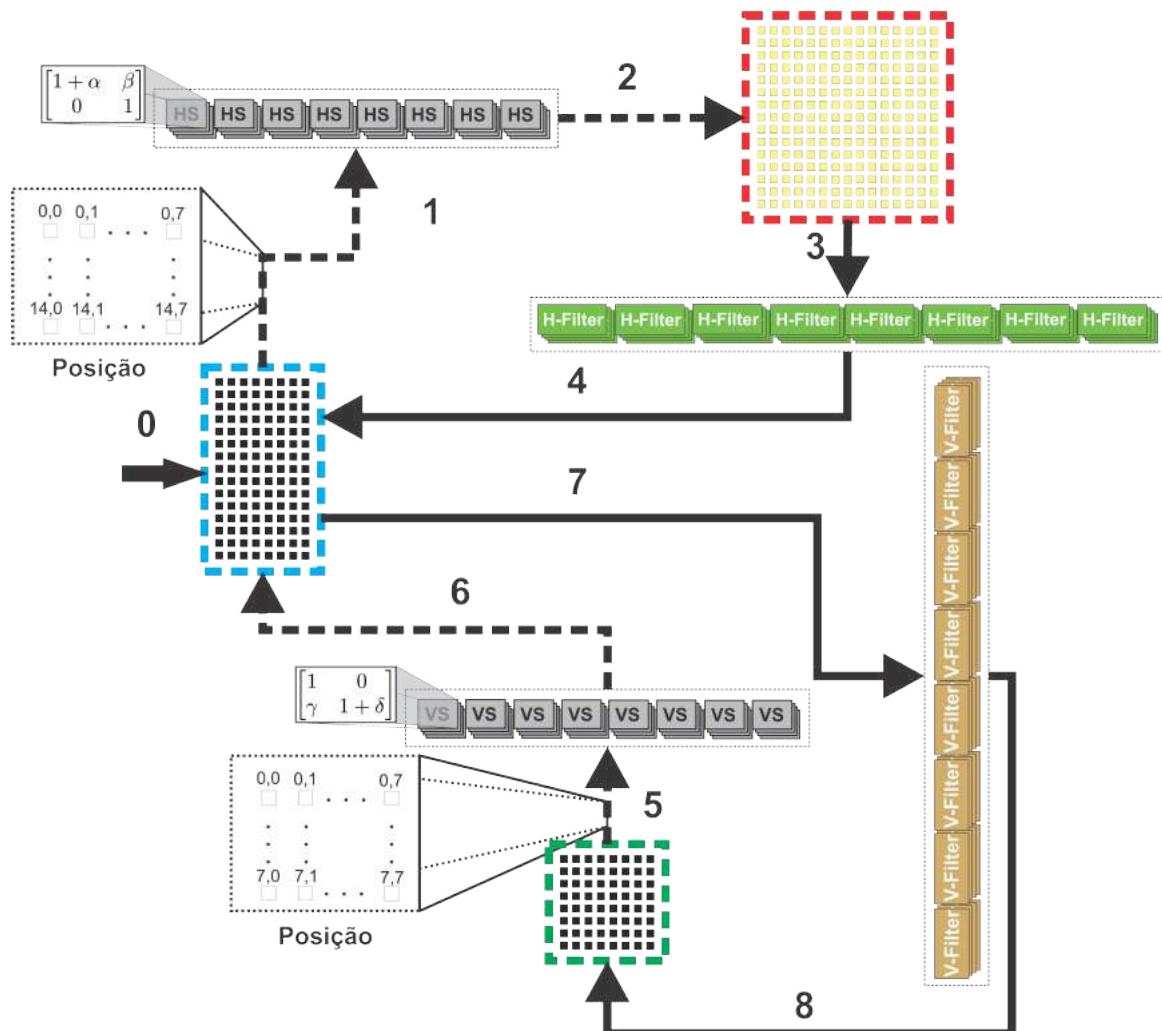

| <b>7.2 Arquitetura para a Compensação de Movimento Distorcido Global</b> . . . . .             | 97  |

| <b>7.2.1 Etapas do Processamento da Compensação de Movimento Distorcido Global</b> . . . . .   | 98  |

| <b>7.2.2 Análise e Resultados</b> . . . . .                                                    | 103 |

| <b>8 CONCLUSÕES</b> . . . . .                                                                  | 104 |

| <b>REFERÊNCIAS</b> . . . . .                                                                   | 106 |

| <b>APÊNDICE A LISTA DE PUBLICAÇÕES REALIZADAS DURANTE ESTA TESE</b> . . . . .                  | 114 |

| <b>A.1 Artigos Publicados em Revistas</b> . . . . .                                            | 114 |

| <b>A.2 Artigos Publicados em Conferências</b> . . . . .                                        | 114 |

# 1 INTRODUÇÃO

Os vídeos digitais estão cada vez mais presentes no mundo inteiro, sejam eles destinados ao lazer ou às atividades profissionais. Devido a esse crescimento, o número de dispositivos móveis capazes de capturar, manipular, armazenar e transmitir esses vídeos digitais cresceu expressivamente. Em pesquisa recente, o *YouTube* indicou que mais de 70% das visualizações de seus vídeos acontecem em dispositivos móveis (YOUTUBE, 2021). Outro ponto relevante para esse debate é que 66,2% da distribuição do volume global mensal de dados móveis diz respeito ao compartilhamento de vídeo (STATISTA, 2022). Essa demanda é impulsionada principalmente pela rápida popularização de mídias sociais, como *Facebook*, *Instagram* e *TikTok*, bem como os serviços de *streaming* de vídeo, como *Youtube*, *Netflix*, *Amazon Prime* e muitos outros que mudaram severamente nossos padrões atuais de entretenimento.

Durante a pandemia do COVID-19 o consumo de vídeos cresceu de forma ainda mais expressiva, pois vários países decretaram *lockdowns*. Já no início de 2020, este episódio proporcionou um aumento de 40,8% no uso das redes sociais, e de 29,6% no consumo de serviços de *streaming* (FASTLY, 2020). Havia uma previsão que o tráfego global de internet crescesse 40% em 12 meses, mas com o COVID-19 isso aconteceu em apenas uma semana (INTERDIGITAL, 2020). Considerando este crescente tráfego de vídeos e o advento de resoluções cada vez maiores, como o *Ultra-high Definition* (UHD) 4K (3840x2160 píxeis) e 8K (7680x4320 píxeis), com crescentes taxas de quadros por segundo, passou a ser um desafio viabilizar a transmissão e o armazenamento destes conteúdos.

Atualmente existem padrões de compressão de vídeo muito eficientes, como o *High-Efficiency Video Coding* ou HEVC (ISO/IEC-JCT1/SC29/WG11, 2013) e o *Versatile Video Coding* ou VVC (FRAUNHOFER, 2021), definidos pela *International Telecommunications Union* (ITU-T) e pela *International Organization for Standardization* (ISO), mas seus usos são dificultados pela quantidade enorme de ferramentas presentes nesses padrões que são patenteadas por diversas empresas. Assim, além do desafio técnico de gerar soluções com elevada eficiência de codificação, surge outros desafios: os custos do uso das soluções existentes no mercado e a dificuldade jurídica

associada ao licenciamento de tantas tecnologias patenteadas (Layek et al., 2017).

Em função destas dificuldades com as tecnologias patenteadas por diversas empresas, várias empresas gigantes como *Google*, *Intel*, *Cisco*, *Mozilla*, *Microsoft*, *Netflix*, *Amazon* e muitas outras formaram a *Alliance for Open Media* (AOMedia), para o desenvolvimento de um novo codec de vídeo livre de royalties chamado AOMedia Video 1 (AV1) (AOMEDIA, 2022).

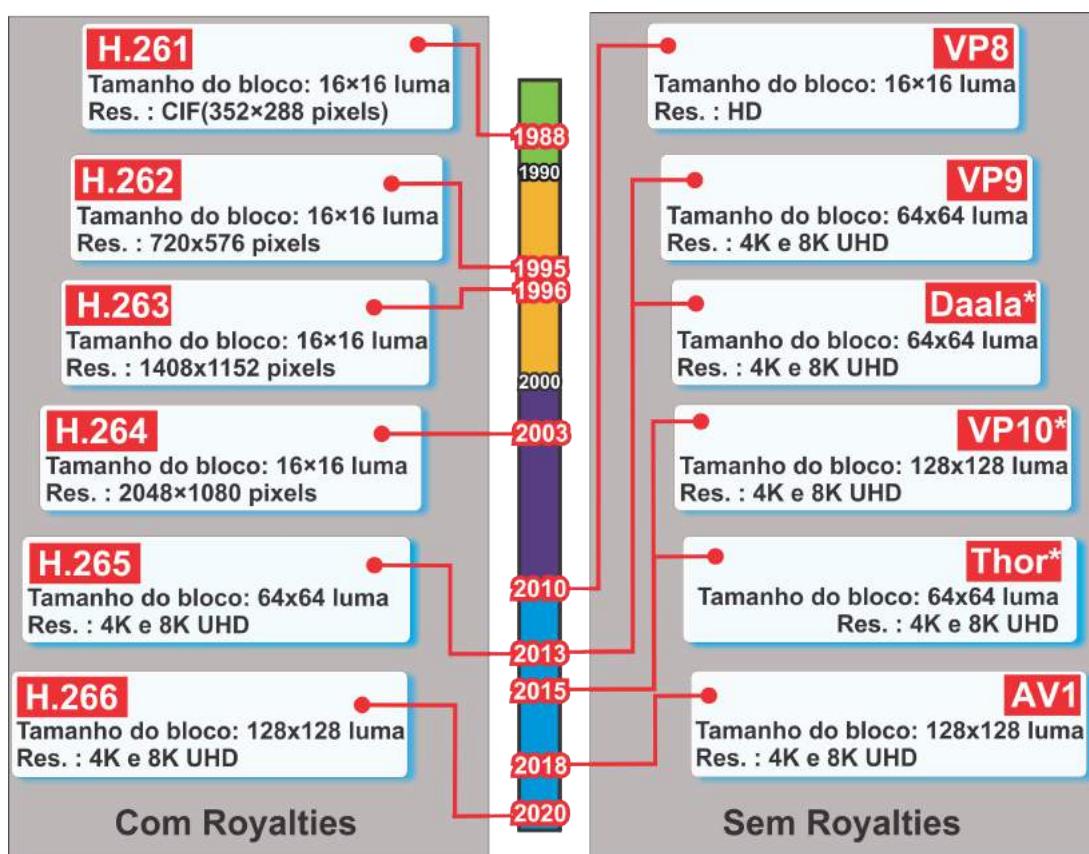

A Figura 1 apresenta a linha do tempo dos codificadores da ITU-T (linha H.26X), onde vários destes padrões são compartilhados com a ISO, como H.262 ou MPEG-2 *Part 2 – Video*, o H.264 ou MPEG-4 *Part 10 Advanced Video Coding* (AVC), o H.265 ou MPEG-H *Part 2 High Efficiency Video Coding* e o H.266 ou MPEG-I *Part 3 - Versatile Video Coding* (VVC). A Figura 1 também apresenta a linha de codificadores que conduziram ao surgimento do AV1, todos livres de royalties.

\* Data que marca o início do desenvolvimento do codificador.

Figura 1 – Linha do tempo de desenvolvimento dos principais codificadores. Fonte: Adaptado de (GOEBEL, 2019).

O H.261 (HUITEMA; TURLETTI, 1996) foi o primeiro codificador padronizado pelo *Video Coding Experts Group* (VCEG) da ITU-T, lançado em 1988, tinha o objetivo de atender a demanda de processamento da sua época. O H.261 processava de forma eficiente as resoluções de até no máximo 352x288 pixels, e amostras de luminância

com blocos de 16x16. Após o H.261, surgiu o H.262 (ou MPEG-2), primeiro padrão de codificação de grande sucesso comercial. Depois do H.262, surgiram o H.263 e o H.264, com o intuito de atender a demanda de novas resoluções de suas épocas. Em 2013 foi lançado o H.265 ou HEVC e, em 2020, foi lançado o H.266 ou VVC, atual estado da arte em codificação de vídeos da ITU-T e da ISO. Estes codificadores estão representados na Figura 1, em ordem cronológica.

O novo padrão de codificação de vídeo da ITU-T e ISO/IEC, o VVC, promete reduzir o tamanho dos arquivos de vídeo em 50% em comparação ao padrão anterior, o H.265, para uma mesma qualidade de vídeo objetiva. O H.266/VVC segue o padrão de compressão do H.265, e foi desenvolvido pela *Joint Video Experts Team* (JVET) com contribuições significativas do departamento de comunicação e aplicativos de vídeo do *Fraunhofer HHI*, em parcerias com empresas como *Sony, Apple, Intel, Huawei, Microsoft, Qualcomm e Ericsson*. O VVC é capaz de processar blocos de 128 x 128 com um particionamento recursivo em árvore quadrática (QT), e para cada folha da QT é permitido um novo particionamento de árvore multi-tipo recursivo (MTT), incluindo partições binárias e ternárias. O VVC é capaz de processar de forma eficiente vídeos de alta resolução, como UHD 4K e 8K, além de ser eficiente na codificação de mídias emergentes, como vídeos omnidirecionais imersivos de 360 graus e vídeos de alta faixa dinâmica (HDR) (FRAUNHOFER, 2021).

Por sua vez, o desenvolvimento do AV1 é uma confluência de três esforços distintos que estavam sendo realizados por empresas da área. De um lado, a Google, com sua linha de codificadores VP<sub>x</sub>, estava preparando a migração do seu conteúdo do VP9 (amplamente usado nos serviços da Google como o *YouTube*) para uma nova versão, chamada de VP10 (Topiwala; Dai; Krishnan, 2016). Por outro lado, foram aproveitados os esforços da *Mozilla* no desenvolvimento do codificador *Daala* (XIPH.ORG, 2018) e da Cisco no desenvolvimento do codificador *Thor* (Bjøntegaard et al., 2016). A primeira especificação de fluxo de bits e decodificação AV1 foi lançada em abril de 2018, que estabeleceu o software de referência *AOMedia Codec* versão 1.0.0, chamado de *libaom* (RIVAZ; HAUGHTON, 2019). Este codificador de vídeo de código aberto foi concebido para ser totalmente isento de royalties e escalável para qualquer dispositivo moderno em qualquer largura de banda. O AV1 é um codificador flexível para uso em conteúdo comercial e não comercial, ideal para projetos de transmissão de vídeo para resoluções UHD, alcançando uma eficiência de compressão até 30% maior que os codificadores livre de royalties que o precederam (AOMEDIA, 2020), (ZABROVSKIY; FELDMANN; TIMMERER, 2018).

Tendo em vista o amplo crescimento do uso de dispositivos embarcados capazes de manipular vídeos, tais como, *smartphones, videogames, tablets*, entre outros, questões como consumo de energia e quantidade de recursos de hardware utilizados são de grande importância. Com base nesses elementos, é possível compreender

que o desenvolvimento de hardware dedicado se mostra uma ótima alternativa, pois um software sendo executado em um Processador de Propósito Geral (GPP - *General Purpose Processor*) ou mesmo em uma Unidade de Processamento Gráfico (GPU - *Graphic Processing Unit*), possui um custo energético proibitivo, além de ser incapaz de atingir tempo real ao processar vídeos de elevada resolução. Desde modo, o projeto de arquiteturas de hardware dedicadas de elevada taxa de processamento torna-se essencial para possibilitar uma adequada relação entre eficiência de codificação e consumo energético, quando o foco são dispositivos que são dependentes de bateria para seu funcionamento.

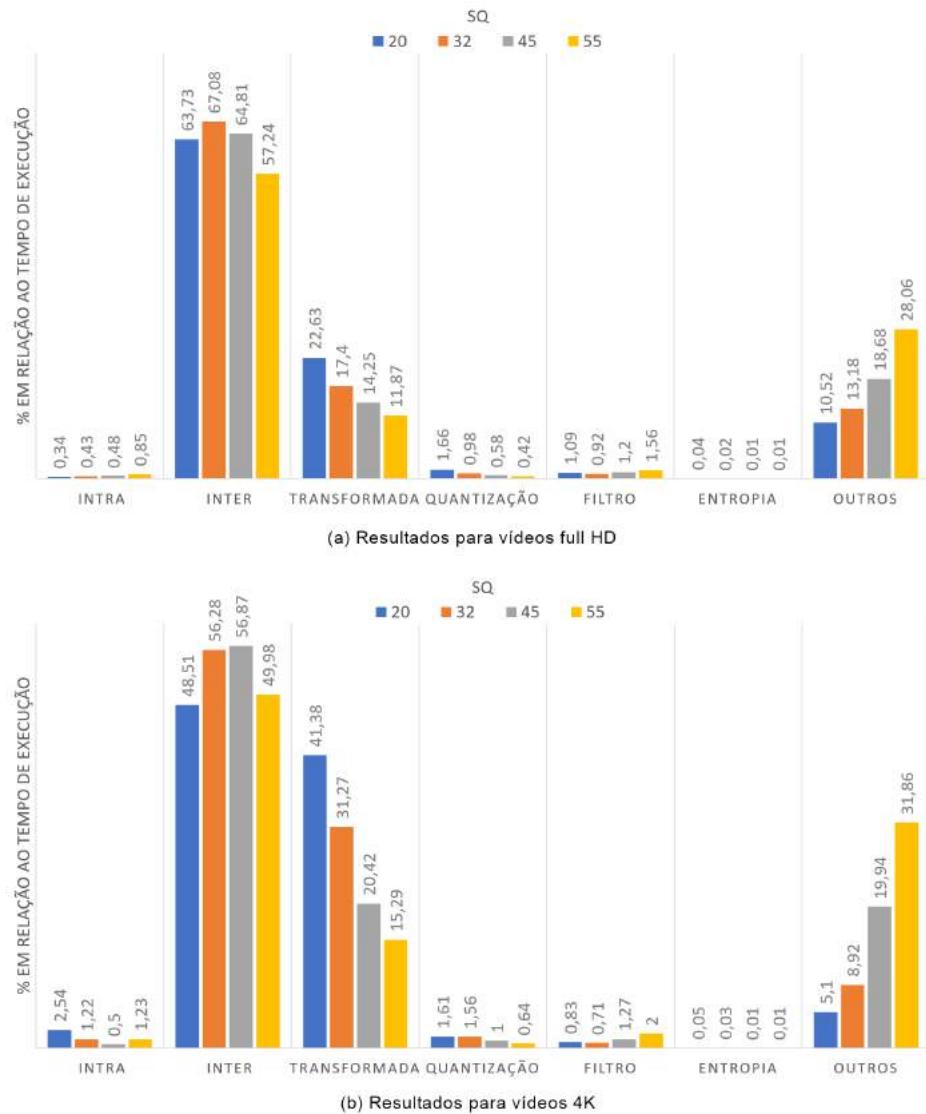

BORGES (2020) apresenta uma análise da distribuição do custo computacional do AV1. O autor descreve que, neste caso, o custo computacional foi avaliado em termos do tempo de processamento exigido em cada módulo, o que equivale ao número aproximado de operações necessárias. A Figura 2 apresenta dois gráficos com um resumo dos resultados percentuais encontrados em (BORGES, 2020), para o tempo de codificação das diversas ferramentas do AV1 (que serão explicadas no próximo capítulo). Assim, a Figura 2 (a) apresenta os resultados para vídeos HD 1080 (1920x1080 píxeis a 60 quadros por segundo), enquanto a Figura 2 (b) apresenta os resultados para vídeos UHD 4K (3840x2160 píxeis a 60 quadros por segundo). Segundo a Figura 2, é possível observar que a predição inter quadros é responsável pelo maior custo computacional nos dois cenários, com 63.21% do tempo de execução para vídeos HD 1080 e 52.66% para vídeos UHD 4K. Desse modo, é possível perceber que a predição inter quadros, como em outros codificadores, é o módulo de maior custo computacional do codificador AV1. Por conta desse elevado custo computacional, a predição inter quadros do AV1 foi escolhida como foco desta tese de doutorado.

O projeto de hardware dedicado é essencial para lidar com o elevado custo computacional da predição inter quadros do AV1, especialmente quando vídeos de alta resolução estão sendo processados por dispositivos móveis. O projeto de hardware nesse cenário deve focar em diversos requisitos, por vezes contraditórios, entre esses, destacam-se:

- a taxa de compressão;

- a qualidade do vídeo;

- a quantidade de recursos de hardware usados;

- a largura da banda de memória;

- a energia consumida;

- a potência dissipada, entre outras (AGOSTINI; SILVA; BAMPI, 2007).

Figura 2 – Percentuais de tempo de execução dos vídeos para cada estágio de codificação para cada CQ Level do codificador AV1 (BORGES, 2020).

A relação entre taxa de compressão e qualidade do vídeo é chamada de eficiência de codificação e o ideal é que as simplificações dos algoritmos usados no projeto de hardware afetem o mínimo possível a eficiência de codificação. Por outro lado, as soluções em hardware devem ser eficientes no uso dos recursos e, principalmente, devem focar em baixo consumo de área e baixa dissipação de potência. Naturalmente, diversos desses requisitos são contraditórios e é importante buscar um balanço adequado entre ganhos e perdas nesses requisitos durante o projeto de hardware dedicado para a codificação de vídeos.

## 1.1 Questão e Hipótese de Pesquisa

Considerando o que foi exposto até aqui, evidencia-se que existe um vasto espaço de pesquisa e desenvolvimento sobre projeto de hardware dedicado para o novo codificador de vídeo da AOMedia, o codificador AV1. Esta presente pesquisa de doutorado começou em 2018, ano em que o formato AV1 foi introduzido, então não existiam trabalhos sobre o AV1 na literatura da época. Dada a relevância do AV1 e as muitas inovações que existem dentro dele, esta tese explora a viabilidade do projeto de arquiteturas de hardware dedicado com a busca de uma elevada eficiência em termos de área e potência para a predição inter quadros do AV1, com foco especial em vídeos de altas resoluções, como UHD 4K e UHD 8K. O foco nas ferramentas usadas na predição inter quadros se dá pelo seu alto custo computacional, conforme apresentado na Figura 2, e na experiência de trabalhos anteriores desenvolvidos no filtro de laço do padrão HEVC. A partir dessa definição inicial, foram elaboradas as questões de pesquisa que norteiam este trabalho:

**Como gerar soluções eficientes em termos de área e potência para as ferramentas da predição inter quadros do formato AV1, capazes de processar vídeos de ultra altas resoluções?**

Com base nessa questão, a hipótese é de que o projeto de hardware dedicado para as ferramentas da predição inter quadros do AV1 explorando paralelismo e o uso de computação aproximada é uma opção viável para atingir as taxas de processamento necessárias para processar vídeos de ultra alta resolução em tempo real e com eficiência em termos de área e potência.

Desde modo, todas as soluções desenvolvidas nesta tese investigam esta hipótese, sendo que cada arquitetura proposta apresenta diferentes desafios, os quais ficarão claros no decorrer deste texto. Os focos de investigação ficaram concentrados na Compensação de Movimento Convencional, na Estimação de Movimento Fracionária e na Compensações de Movimentos Distorcidos Local e Global, uma vez que não foi possível, por conta do tempo disponível para o desenvolvimento desta tese, também investigar as outras ferramentas da predição inter quadros do AV1. Estas ferramentas de codificação, bem como as soluções em hardware desenvolvidas serão detalhadas no decorrer deste texto.

Ao final do trabalho foi possível demonstrar que a hipótese apresentada acima é totalmente válida para as ferramentas investigadas neste trabalho.

Conforme já mencionado anteriormente, para além das publicações geradas a partir desta tese, ainda não existem outros trabalhos na literatura que possam ser comparados com as soluções desenvolvidas e apresentadas neste texto. Isso demonstra a novidade das soluções propostas e apresentadas nesse trabalho.

## 1.2 Objetivos e Contribuições

O objetivo geral deste trabalho é explorar a viabilidade de construção de hardware dedicado e com eficiência em termos de área e potência para a predição inter quadros do AV1, quando processando vídeos com altas resoluções (UHD 4K e 8K), explorando técnicas de computação aproximada em conjunto com técnicas de projeto de hardware de baixo consumo.

O foco desta tese está no desenvolvimento de novas arquiteturas de hardware para algumas das ferramentas da predição inter quadros do AV1, conforme descrito abaixo, onde também são resumidos os principais métodos utilizados, bem como as publicações geradas a partir de cada solução:

1. Desenvolvimento da Compensação de Movimento (*Motion Compensation* - MC) do codificador AV1 usando apenas somadores e deslocadores, ao invés de multiplicadores (método original) e usando diferentes níveis de paralelismo. Essa solução foi publicada em (Domanski et al., 2019) e está apresentada em detalhes no Capítulo 5 deste texto.

2. Desenvolvimento do interpolador da Estimação de Movimento Fracionária (*Fractional Motion Estimation* - FME) do AV1 explorando computação aproximada em dois níveis e também implementando os filtros originais (para comparação). Esse trabalho foi publicado em (DOMANSKI et al., 2021) e selecionado entre os quatro melhores da *track* de *Multimedia Systems and Applications*. Esta solução está apresentada em detalhes no Capítulo 6 deste texto.

3. Desenvolvimento de hardware visando o processo completo da FME do AV1, com base nos filtros originais da FME. Esse trabalho foi publicado em (DOMANSKI et al., 2023a) e está apresentado em detalhes no Capítulo 6 do texto.

4. Desenvolvimento de hardware para o Modo de Compensação de Movimento Distorcido Local (*Warped Local*), que está detalhada no Capítulo 7 e ainda não publicados. Essa solução, usa um interpolador com 192 filtros. A arquitetura foi desenvolvida usando apenas somadores e deslocadores, ao invés de multiplicadores (método original), e em diferentes níveis de paralelismo.

5. Desenvolvimento de hardware para o Modo de Compensação de Movimento Distorcido Global (*Warped Global*), que também está detalhada no Capítulo 7 deste texto. A *Warped Global* do AV1 também foi desenvolvida substituindo os multiplicadores por somadores e deslocadores. Esta solução ainda não foi enviada para publicação.

### 1.3 Apresentação do Texto

O restante deste texto está organizado da seguinte forma: O capítulo 2, apresenta uma introdução sobre codificação de vídeo e o codificador AV1. O capítulo 3, apresenta uma revisão sobre os conceitos empregados nesse trabalho, mais especificamente sobre a predição inter quadros do codificador AV1. O capítulo 4, apresenta os trabalhos encontrados na literatura sobre o tema da tese. O capítulo 5, apresenta o desenvolvimento da arquitetura e os resultados obtidos para a Compensação de Movimento do AV1. O capítulo 6, apresenta o desenvolvimento da arquitetura e os resultados obtidos para a Estimação de Movimento Fracionária do AV1. O capítulo 7, apresenta as arquiteturas desenvolvidas para as etapas da *Warped Motion* (Local e Global) e os resultados respectivos destas arquiteturas. Por fim, o capítulo 8, apresenta as conclusões dessa tese.

## 2 CONCEITOS DE COMPRESSÃO DE VÍDEOS E O FORMATO AV1

O vídeo digital é composto por uma série de imagens estáticas (chamadas de quadros ou *frames*), onde cada imagem individual não possui movimento próprio; porém, apresentadas ao espectador sequencialmente, em uma taxa temporal específica, fornecem uma sensação de movimento suficientemente alta para garantir uma percepção visual suave sem transições. Normalmente, a taxa de quadros para garantir a percepção suave do movimento é de cerca de 30 quadros por segundo (*Frames per Second - fps*), levando em consideração o Sistema Visual Humano (*Human Visual System - HVS*) (RICHARDSON, 2003). Entretanto, as aplicações de vídeo atuais apresentam requisitos mais elevados, aumentando a necessidade de taxas de quadros para até 120 fps, a fim de fornecer vídeos digitais com uma percepção realista de movimento, especialmente para resoluções mais elevadas, como UHD 4K e 8K.

Cada quadro é representado por uma matriz de píxeis bidimensionais, com dimensões  $W \times H$ , sendo  $W$  a dimensão horizontal (largura) e  $H$  a dimensão vertical (altura), denominada resolução espacial do vídeo.

Os píxeis armazenam informações de cor e brilho para sua posição correspondente dentro de cada quadro. Para vídeos coloridos, um pixel é composto por três amostras de cor. Vários espaços de cor definem essa representação numérica de propriedades de pixel, como, por exemplo, o YCbCr (luminância, crominância azul e crominância vermelho), amplamente usado nos codificadores de vídeo (RICHARDSON, 2002).

É fácil imaginar que, em uma série de quadros sequenciais de um vídeo, existam muitas semelhanças entre os quadros. Essas semelhanças são chamadas de redundância temporal, uma vez que existe uma grande quantidade de informações repetidas no tempo na representação de vídeos. Também há o que é chamado de “redundância espacial”, pois píxeis vizinhos em um quadro tendem a ser semelhantes. Assim, os vídeos não comprimidos possuem elevada redundância em termos de textura (temporal e espacial) (SHI; SUN, 2017). Por fim, existe também a redundância entrópica, que diz respeito às probabilidades de ocorrência dos símbolos nos vídeos.

Deste modo, armazenar vídeos sem compressão, ou seja, armazenar vídeos

cheios destas redundâncias, consome muito espaço de armazenamento, e transmitir esses vídeos consome uma elevada largura de banda (CHEN; CRANTON; FIHN, 2016).

Portanto, os codificadores de vídeo procuram reduzir essas redundâncias, para que menos espaço de armazenamento seja usado e uma menor largura de banda seja consumida ao representar e transmitir esses vídeos. Essa redução, foca no descarte de dados redundantes ou irrelevantes para o HVS, visando transmitir apenas os dados necessários para descrever as informações relevantes do vídeo. Dessa maneira, os codificadores de vídeo conseguem reduzir, de maneira significativa, a quantidade de dados necessários para representar um vídeo (SHI; SUN, 2017).

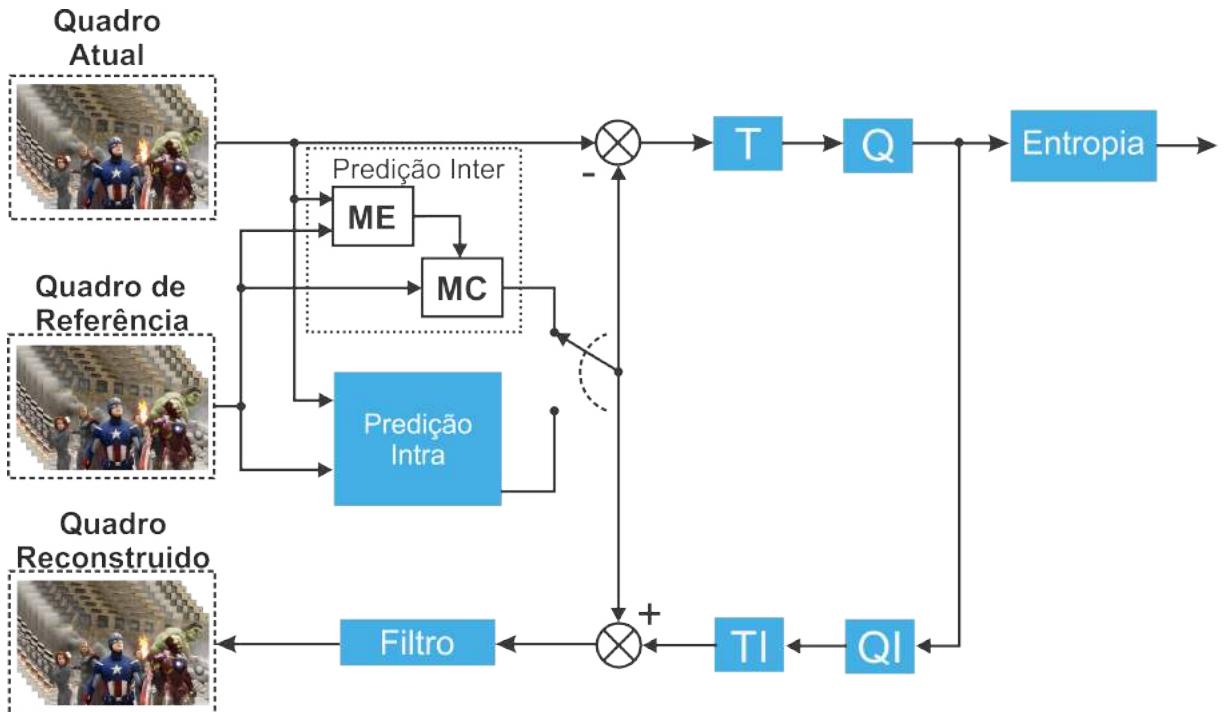

Os codificadores atuais seguem um modelo chamado de codificação híbrida. As principais etapas de processamento de um codificador híbrido, incluindo o AV1, estão representadas na Figura 3. Inicialmente, cada quadro do vídeo de entrada é dividido em blocos, que são processados de forma independente. Então, cada bloco passa por uma etapa de predição, que pode ser intra quadro, que busca redundâncias de informações dentro do mesmo quadro, ou inter quadros, que busca por redundâncias em quadros anteriormente processados. É importante salientar que as predições não são perfeitas, o que leva a geração de resíduos, através da subtração do resultado da predição e o bloco original. Os resíduos, por sua vez são processados pela etapa de “transformadas” (T na Figura 3) e “quantização” (Q na Figura 3). As transformadas transformam a representação dos resíduos para o domínio das frequências e, nesse domínio, a quantização elimina ou atenua as frequências para as quais o sistema visual humano é menos sensível. Esse processo de quantização gera perdas de informação e, quanto maior a perda, maior a taxa de compressão e menor a qualidade visual do vídeo; então, os codificadores atuais possuem algum tipo de controle para seleção do ponto de operação ideal na quantização. Finalmente, a informação quantizada é processada pelo codificador de entropia, que reduz a redundância entrópica na representação dos símbolos de entrada. Após a codificação de entropia, os dados estão prontos para serem transmitidos ou armazenados. Como a etapa de quantização gera perdas de informação, para garantir que o codificador e o decodificador usem as mesmas referências, o codificador possui as etapas de quantização e transformadas inversas (QI e TI na Figura 3). O resultado da quantização inversa é novamente somado ao bloco original, para gerar o bloco reconstruído. Finalmente, o bloco reconstruído passa por uma etapa de filtragem, a fim de reduzir artefatos inseridos nos vídeos, no processo de codificação. Então o bloco é armazenado para ser usado como referência para predições futuras (GOEBEL, 2019).

Figura 3 – Diagrama de blocos genérico de codificação de vídeo. Fonte: Adaptado de (AGOSTINI; SILVA; BAMPI, 2007).

## 2.1 Codificador de Video AV1

Em meados de 2015, algumas empresas como a *Google*, *Apple*, *Cisco*, *Samsung*, *IBM*, e mais um conjunto de 30 empresas líderes, de alta tecnologia, fundaram a *Alliance for Open Media* (AOMedia), para trabalhar em conjunto no objetivo de desenvolver um codificador de vídeo aberto de próxima geração que foi chamado de *AOMedia Video 1* ou *AV1* (AOMEDIA, 2012). Seu desenvolvimento partiu do princípio do aprimoramento das ferramentas do VP9 (Mukherjee et al., 2013) do Google, adicionando algumas inovações propostas nos codificadores *Thor* (Bjøntegaard et al., 2016) e *Daala* (XIPH.ORG, 2018), da *Cisco* e da *Mozilla*, respectivamente, ambas empresas integrantes do *AOMedia*. Em seguida, novas ferramentas de codificação foram propostas, testadas, discutidas e incorporadas no codec da *AOMedia*. No decorrer dos anos, algumas versões de testes foram lançadas e, em meados de 2018, a primeira versão do AV1 foi lançada, incorporando uma variedade de novas ferramentas de compressão, além de recursos de alto nível, projetados para casos de uso específicos. O codificador AV1 foi criado com o intuito de: (i) proporcionar a entrega de vídeo em tempo real, em alta qualidade, (ii) ter escalabilidade para dispositivos modernos em várias larguras de banda, (iii) ter um bom desempenho computacional, (iv) ser adequado para ser otimizado para hardware e (v) buscar flexibilidade para conteúdos comerciais e não comerciais (Chen et al., 2018).

As próximas seções apresentam as principais características do AV1.

### 2.1.1 Partição de Blocos

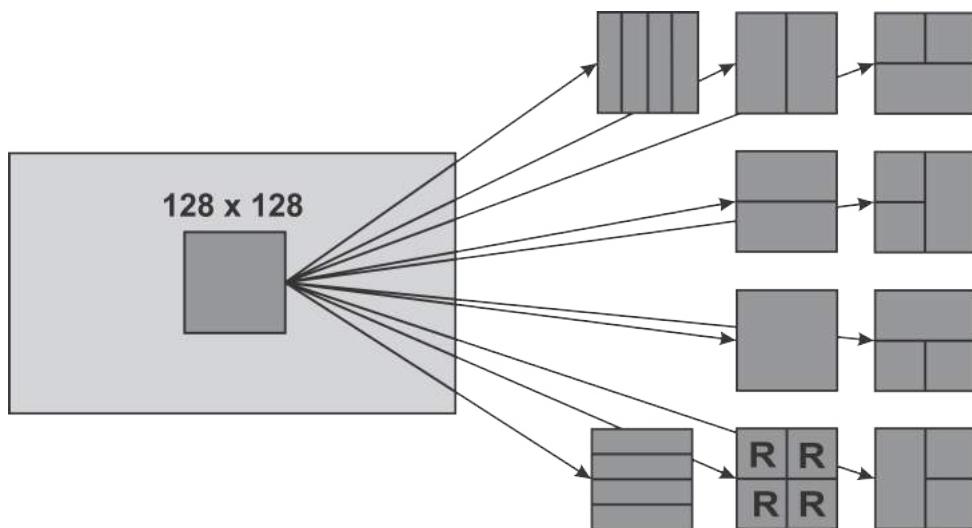

O AV1 segue o mesmo modelo de codificação híbrida baseado em blocos, que já foi apresentado. Inicialmente, cada quadro é dividido em blocos de tamanhos iguais, chamados de *SuperBlocks* (SB), que podem ter tamanhos de 128 x 128 ou 64 x 64 píxeis.

Os SBs podem ser divididos em tamanhos menores, visando seu processamento. Todos os tipos de particionamento que o codificador AV1 suporta, estão apresentados na Figura 4 (Chen et al., 2018).

Figura 4 – Particionamento do codificador AV1. Fonte: Adaptado de (Chen et al., 2018).

O processo de partição de blocos gera uma árvore, onde o SB é a raiz desta árvore. Sempre que um bloco quadrático é considerado (blocos R na Figura 4), esse bloco pode ser subdividido, recursivamente, nos vários tipos de blocos permitidos pelo AV1 e apresentados na Figura 4.

Observando a Figura 4 é possível perceber que o bloco pode ser particionado de forma retangular em dois blocos, verticais ou horizontais. Outro modo de subdivisão do bloco é de maneira assimétrica e, neste caso, os blocos são particionados em quatro blocos com tamanhos idênticos, sendo a orientação das suas partições retangulares de 4:1 ou 1:4. Por último, existe o particionamento tipo T. Neste tipo de particionamento sempre serão gerados três blocos: dois blocos quadrados e um bloco retangular. Nenhuma destas partições não quadráticas pode ser subdividida em novos blocos.

O processo recursivo de particionamento tem sua condição de parada no tamanho de bloco de 4 x 4 amostras para luminância, que é o menor tamanho de bloco suportado no codificador AV1. Considerando a subamostra de informações de crominância suportada pelo AV1, em alguns casos bem específicos, os blocos de crominância podem ter tamanho mínimo de 2 x 2 amostras (GOEBEL, 2019) (HAN et al., 2021).

Existem ainda algumas situações especiais que restringem o particionamento em alguns casos. As partições assimétricas 1:4 e 4:1 não estão disponíveis para blocos 128 x 128 e 8 x 8 e os blocos 8x8 não podem ser particionados em T (Chen et al., 2019).

Com base nessas informações, é possível concluir que o AV1 pode suportar até 22 tamanhos de blocos, no processo de codificação para as amostras de luminância (Chen et al., 2019), partindo do pressuposto que o SB inicial possui 128 x 128 amostra de luminância. Deste modo, os tamanhos de blocos suportados são: 128 x 128, 128 x 64, 64 x 128, 64 x 64, 64 x 32, 64 x 16, 32 x 64, 16 x 64, 32 x 32, 32 x 16, 32 x 8, 16 x 32, 8 x 32, 16 x 16, 16 x 8, 16 x 4, 8 x 16, 4 x 16, 8 x 8, 8 x 4, 4 x 8 e 4 x 4 (AOMEDIA, 2020).

### 2.1.2 Predição Intra Quadro

A etapa de predição intra quadro do AV1 é encarregada de reduzir a redundância espacial encontrada nos quadros de um vídeo, sendo ela associada à correlação entre as amostras especialmente próximas de um mesmo quadro. Como as amostras vizinhas costumam ser muito semelhantes, ao invés de representar amostras individuais, separadamente, as amostras de cada bloco são representadas por texturas e arestas direcionais de amostras vizinhas, já processadas. Dessa forma, é possível reduzir o número de bits necessários para representar um quadro. Esta etapa acontece dentro de um quadro, e ocorre sem a necessidade de usar outros quadros como referência (BULL; ZHANG, 2021).

O codificador AV1 oferece mais modos de predição que seu antecessor, o VP9, tendo um total de 69 modos de predição intra. Esta etapa é explorada de várias formas e é um dos módulos mais inovadores no AV1. Para maiores ganhos de taxa de compressão, o AV1 define novos modos de predição, novas ferramentas e melhora alguns modos de predição, que já existiam no padrão HEVC ou no VP9 (GOEBEL, 2019). Melhorias são definidas no *Intra Orientation Prediction*, que passa a explorar mais tipos de redundância espacial em texturas direcionais. O modo *in-direction* é estendido para variar ângulos com ajuste de granularidade mais fino, e outra novidade, é aplicar um filtro passa-baixa aos valores da amostra antes de realizar a predição do bloco (Chen et al., 2018).

Já os modos não direcionais ganharam um número maior de preditores, como *Smooth*, *paeth*, *Chroma-from-Luma*, *Recursive-based-filtering Mode* e *DC*, os quais proporcionam uma melhor detecção da redundância espacial e, consequentemente, melhores taxas de compressão. Outra inovação que o AV1 trouxe na predição intra, são os modos: *Intra Block Copy* (Intra - BC) e o *Color Palette*, direcionados para vídeos de conteúdo de tela (Chen et al., 2018).

### 2.1.3 Predição Inter Quadros

A predição inter quadros explora a redundância temporal de um vídeo e precisa referenciar outros quadros, para realizar a predição. Portanto, a redundância temporal está diretamente relacionada entre as amostras de quadros sucessivos no vídeo, pois quadros próximos tendem a ter um nível de similaridade muito elevado, o que implica em uma alta semelhança entre as amostras ao longo do tempo. Sendo assim, são aplicadas ferramentas para que seja possível estimar a redundância temporal, e são usados vetores de movimento para sinalizar mudanças nas posições dos blocos ao longo do tempo. Com a estimativa realizada, entra em cena um processo de compensação de movimento, que é usado para ajustar o conteúdo do quadro de referência, de acordo com o modelo de movimento e, assim, gerar o bloco atual reconstruído (SHI; SUN, 2017), que será subtraído do bloco original para gerar os resíduos.

O AV1 usa de inúmeras ferramentas que o auxiliam na estimação da redundância temporal, como as listadas abaixo:

- Estimação de Movimento Inteira: A Estimação de Movimento Inteira (*Integer Motion Estimation* - IME) é empregada exclusivamente no codificador com base no canal de luminância. Para cada segmento do SB particionado, a IME deve localizar, em um ou mais quadros de referência, o segmento que mais se assemelha ao segmento atual;

- Estimação de Movimento Fracionária: A Estimação de Movimento Fracionária (*Fracional Motion Estimation* - FME) é executada com o intuito de refinar o resultado encontrado na FME com a busca de movimentos mais suaves. Portanto, a FME é um processo que gera subamostras fracionárias em torno das amostras inteira;

- Compensação de Movimento Convencional: A Compensação de Movimento (*Motion Compensation* - MC) convencional é responsável por reconstruir os blocos previstos pela etapa da Estimação de Movimento;

- Compensação de Movimento de Bloco Sobreposto: No AV1 foi definido um algoritmo de compensação de movimento que minimiza os erros de previsão próximos às bordas do bloco, denominado Compensação de Movimento de Bloco Sobreposto (*Overlapped Block Motion Compensation* - OBMC). A OBMC é capaz de explorar as informações dos MV vizinhos espaciais mais próximos melhorando, assim, a qualidade de predição ao redor das bordas;

- Compensação de Movimento Distorcido: O AV1 implementa a Compensação de Movimento Distorcido (*Warped Motion Compensation* - WMC), com o intuito de

trazer melhorias a eficiência de codificação, que tem por base as transformações afim (*affine*);

- Modo de Predição Composta Avançada: A predição composta avançada tem como ideia principal gerar uma média ponderada entre duas predições diferentes do mesmo bloco, mais a máscara (peso) para, assim, resultar em uma predição final.

As ferramentas da predição inter quadros, que são foco deste trabalho, serão discutidas em maiores detalhes no Capítulo 3 desta tese.

#### 2.1.4 Transformadas e Quantização

As etapas de predição intra quadros e inter quadros geram resíduos que precisam ser codificados. Esses resíduos passam pelas Transformadas e Quantização para, posteriormente, passarem pelo processo de codificação de Entropia.

As Transformadas têm como objetivo transformar os resíduos das predições intra ou inter quadros do domínio espacial para o domínio das frequências, preparando, assim, os dados para a quantização. O AV1 permite o uso de até quatro tipos diferentes de transformadas, e são elas: (i) a Transformada Discreta do Cosseno - *Discrete Cosine Transform* (DCT), (ii) a Transformada Discreta do Seno Assimétrica - *Asymmetric Discrete Sine Transform* (ADST), (iii) a Transformada Discreta do Seno Assimétrica Invertida - *Flipped Asymmetric Discrete Sine Transform* (FlipADST) e (iv) a Transformada Identidade - *Identity Transform* (IDTX) (Chen et al., 2018). Usando o princípio da separabilidade, transformadas diferentes podem ser usadas no sentido horizontal e vertical do bloco, como por exemplo DCTxADST (GOEBEL, 2019). Além disso, para blocos preditos pela predição intra, uma segunda etapa de transformadas pode ser aplicada, através da transformada denominada *Low Frequency Non-Separable Secondary Transform* (LFNSST) (ZHAO et al., 2016).

Já a etapa de Quantização ocorre após a etapa da Transformada ser concluída, e tem como principal objetivo reduzir informações imperceptíveis ao sistema visual humano. A etapa de Quantização é realizada no domínio das frequências, porém, ao contrário da Transformadas, a Quantização é um processo que gera perdas (CHEN; CRANTON; FIHN, 2016). Essas perdas são função do parâmetro de quantização, denominado *Constrained Quality* (CQ), que varia de 0 a 63 (HAN et al., 2021), cujo valor é ajustado para atender a eficiência de codificação desejada, ou seja, a relação entre o tamanho do arquivo e a qualidade do vídeo.

#### 2.1.5 Codificação de Entropia

A etapa de codificação de entropia é uma técnica que visa a eliminação da redundância entrópica, ela é responsável por reduzir o número de bits necessários para

representar o *bitstream* produzido pelo codificador, reduzindo, assim, a redundância na representação dos símbolos. A representação dos símbolos é modificada com o uso de codificação de comprimento de palavra variável (AFONSO; AGOSTINI; SUSIN, 2019).

O AV1 utiliza o método *symbol to symbol adaptive multi-symbol* para comprimir os elementos da sintaxe, sendo que cada elemento é considerado um membro de um alfabeto específico, de N elementos e o contexto de entropia, consiste em um conjunto de N probabilidades que, por sua vez, são armazenadas em funções de distribuição cumulativa *Cumulative Distribution Function* (CDF). Um bloco ou quadro pode conter vários contextos de entropia, sendo que cada bloco escolhe o contexto de entropia que irá usar, com base nos modos selecionados pelos blocos vizinhos que, por sua vez, utilizam um codificador de entropia chamado Codec Booleano para codificar o fluxo de bits inteiro (Chen et al., 2018).

### 2.1.6 Filtragem de Laço

A etapa de Filtragem de Laço é responsável por reduzir os artefatos inseridos no vídeo durante todo o processo de codificação pois, como o processo de codificação é baseado em blocos, certos artefatos visuais podem surgir como descontinuidades entre blocos vizinhos (PALAU et al., 2022).

O codificador AV1 estabelece o uso de três filtros de laço, sendo eles o Filtro de Deblocagem - *Deblocking Filter* (DBF), Filtro de Aprimoramento Direcional Restrito - *Constrained Directional Enhancement Filter* (CDEF) e o Filtro de Restauração de Laço Comutável - *Switchable Loop Restoration Filter* (SLRF) (Han; Chiang; Xu, 2017).

## 2.2 Métricas de Avaliação

Na literatura existem diversas métricas que visam avaliar a eficiência da codificação de vídeos. Dentre todas essas métricas, existem duas principais abordagens em suas análises, que podem ser objetiva e subjetiva. Sendo que, as métricas que tem uma abordagem objetiva usam de modelos matemáticos para realizar a comparação entre o vídeo original e o vídeo modificado (codificado). Já as métricas que se baseiam em avaliações subjetivas levam em conta a percepção do usuário. Neste trabalho, são usada apenas métricas objetivas.

O *Peak Signal-to-Noise Ratio* (PSNR) foi o método objetivo usado neste trabalho, uma vez que este é o método mais usado pela comunidade da área. Este é um método que utiliza de métricas de comparações de similaridade entre dois sinais baseada em MSE (erro quadrático médio) (BULL; ZHANG, 2021). Sua medida é feita em decibéis (dB), e, quanto maior seu valor, maior a similaridade entre os sinais.

Entretanto, ponderar a eficiência de um codificador não é simples, pois existem

vários padrões de codificação, e cada um pode usar métricas e parâmetros diferentes. Para resolver este problema é necessário comparar diferentes sinais, de forma justa e ponderada e em igualdade de condições. As métricas mais comuns para definir a eficiência da codificação são *Bjøntegaard Delta PSNR* (BD-PSNR) e *Bjøntegaard Delta Bit Rate* (BD-BR), que medem a qualidade dos sinais (PSNR) e a quantidade de dados necessários para representá-los (taxa de bits).

O BD-PSNR busca calcular a diferença média da variação do PSNR (em decibéis) quando um codificador âncora e um codificador sob avaliação atingem a mesma taxa de bits (*bitrate*) (BJONTEGARD, 2001). Um valor negativo de BD-PSNR significa perda de eficiência de codificação (menor qualidade para a mesma taxa de bits), enquanto um valor positivo implica em uma melhoria na eficiência de codificação (maior qualidade para a mesma taxa de bits).

Já o BD-BR computa a variação percentual da taxa de bits entre o codificador âncora e o codificador sob avaliação, considerando vídeos com a mesma qualidade objetiva (PSNR) após a codificação (BJONTEGAARD, 2008). Neste caso, um BD-BR positivo significa perda de eficiência de codificação (maior taxa de bits para a mesma qualidade), enquanto um BD-BR negativo implica em um ganho na eficiência de codificação (menor taxa de bits para a mesma qualidade).

Para a realização do cálculo dessas métricas são fundamentais amostras diferentes de um mesmo sinal. Sendo que, a eficiência de codificação de uma solução é codificada para quatro parâmetros diferentes de *Constrained Quality* (CQ), segundo os documentos que definem as condições comuns de teste (ZEN, 2020).

## 3 FERRAMENTAS DA PREDIÇÃO INTER QUADROS DO CODIFICADOR AV1

Neste capítulo estão apresentadas, com mais detalhes, as ferramentas da predição inter quadros do codificador AV1 que são foco desta tese. Assim, será dado destaque para as etapas da Estimação de Movimento Fracionária, da Compensação de Movimento Convencional e da Compensação de Movimento Distorcido, que compõem o módulo da predição inter quadros do codificador AV1. Como também, um breve detalhamento sobre a etapa da Estimação de Movimento Inteira para facilitar o entendimento das demais etapas.

### 3.1 Estimação de Movimento

A predição inter quadros do codificador de vídeo AV1, igualmente aos demais codificadores, é composto principalmente pela etapa Estimação de Movimento (*Motion Estimation* - ME) que tenta identificar e eliminar redundâncias temporais entre os quadros sucessivos que formam uma imagem dinâmica. Essas redundâncias temporais podem ser observadas de diferentes maneiras. Um exemplo prático seria o deslocamento de um carro por uma pista. O fundo (pista) se mantém sem o movimento por vários quadros, considerando que a câmera permaneça parada, já o carro, sofre um pequeno deslocamento da sua posição em relação aos demais quadros. Sendo assim, após o primeiro deslocamento, a diferença entre os quadros sucessivos seria somente a posição do carro a cada instante. Portanto, a ME é empregada para investigar essas semelhanças e, em seguida, prevê o quadro atual, que está sendo codificado, usando quadros de referência.

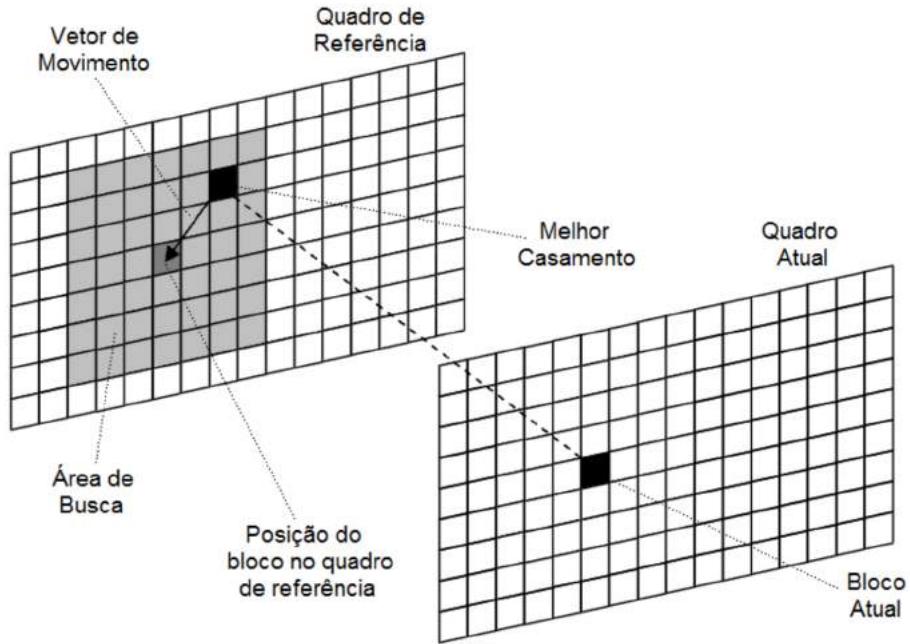

Para prever o quadro atual ele é dividido em blocos, que são comparados com os blocos do quadro de referência, conforme é possível ver na Figura 5. Para essa comparação, um critério de similaridade é empregado aos blocos de uma área de busca no quadro de referência, o qual geralmente fica ao redor a posição original. Porém, nada impede que a área de busca seja definida a partir de outro ponto, o que proporciona uma maior probabilidade de aproximação da posição original, além de

reduzir a complexidade computacional quando comparado à área total de um quadro (AFONSO; AGOSTINI; FRANCO, 2013). A seguir, é gerado um Vetor de Movimento (*Motion Vector - MV*) que direcionará o bloco que gerou o melhor casamento com o bloco atual, ou seja, a maior similaridade entre o bloco do quadro atual e o bloco de referência.

Figura 5 – Elementos presentes na Estimativa de Movimento (AFONSO; AGOSTINI; FRANCO, 2013).

Para alcançar esse resultado esperado, a ME é executada em duas etapas: Estimação de Movimento Inteira (*Integer Motion Estimation - IME*) e Estimação de Movimento Fracionaria (*Fracional Motion Estimation - FME*).

### 3.1.1 Estimação de Movimento Inteira

A Estimação de Movimento Inteira (*Integer Motion Estimation - IME*), é aplicada no codificador considerando apenas informações de luminância. Para cada bloco, a IME deve localizar, em um ou mais quadros de referência, qual bloco mais se assemelha ao bloco atual. Após a IME encontrar o melhor bloco no quadro de referência, ela gera um Vetor de Movimento (MV), indicando a posição deste bloco no quadro de referência. Os MV são definidos como vetores de duas dimensões ( $x, y$ ) e indicam o deslocamento espacial de um bloco em um determinado quadro, em relação à posição do bloco atual no quadro atual.

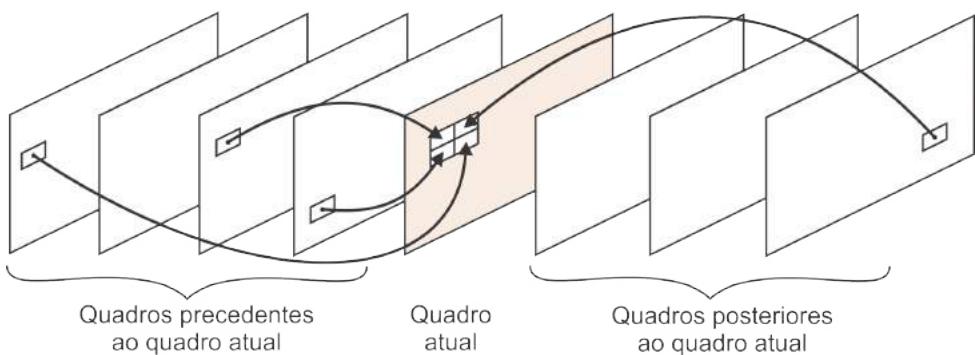

O codificador AV1 permite o uso de múltiplos quadros de referência, permitindo um máximo de oito quadros em seu *buffer* de quadro decodificado. O quadro atual a ser codificado pode escolher qualquer um entre os sete possíveis quadros para usar

como seu quadro de referência. O codificador é capaz de atribuir explicitamente, a cada referência, um índice de quadro de referência exclusivo, variando de 1 a 7. Os quadros de referência com índice 1 a 4 são designados para os quadros que precedem o quadro atual, enquanto os quadros de índice 5 a 7 são para referências posteriores ao quadro atual, em relação a ordem de exibição (HAN et al., 2021). Isso é possível pois o AV1, como outros codificadores atuais, permite o processamento dos quadros fora da ordem de captura, uma vez que, antes de ser usado como referência, o quadro precisa ter sido codificado. Esse processo está apresentado na Figura 6.

Figura 6 – Exemplo de uso de múltiplos quadros de referência.

Para encontrar o melhor bloco no quadro de referência, a IME utiliza um algoritmo de busca. Esses algoritmos variam, desde a busca exaustiva, até algoritmos sub ótimos (algoritmos rápidos), que visam reduzir a complexidade da IME. Entretanto, estes algoritmos rápidos podem introduzir impactos negativos em relação à eficiência da codificação (AGOSTINI; SILVA; BAMPI, 2007).

Além dos algoritmos de busca, a IME utiliza um critério de similaridade para decidir qual é o melhor casamento na procura sobre o quadro de referência. A soma de diferenças absolutas (*Sum of Absolute Differences* - SAD) (Vanne et al., 2006), é o critério mais usado para essa função, principalmente para projetos em hardware. O SAD consiste na soma das diferenças absolutas entre as amostras do bloco atual e as amostras do bloco candidato do quadro de referência. Deste modo, o bloco candidato que atingir o menor SAD será escolhido para representar o bloco atual. A Equação 1 define o cálculo do SAD, sendo  $R$  as amostras do bloco de referência e  $O$  as amostras do bloco do quadro de referência.

$$SAD = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} |R_{i,j} - O_{i,j}| \quad (1)$$

### 3.1.2 Estimação de Movimento Fracionária

Assim que o melhor vetor de movimento na etapa da IME é encontrado para o bloco atual, a Estimação de Movimento Fracionária (*Fractional Motion Estimation* - FME) é

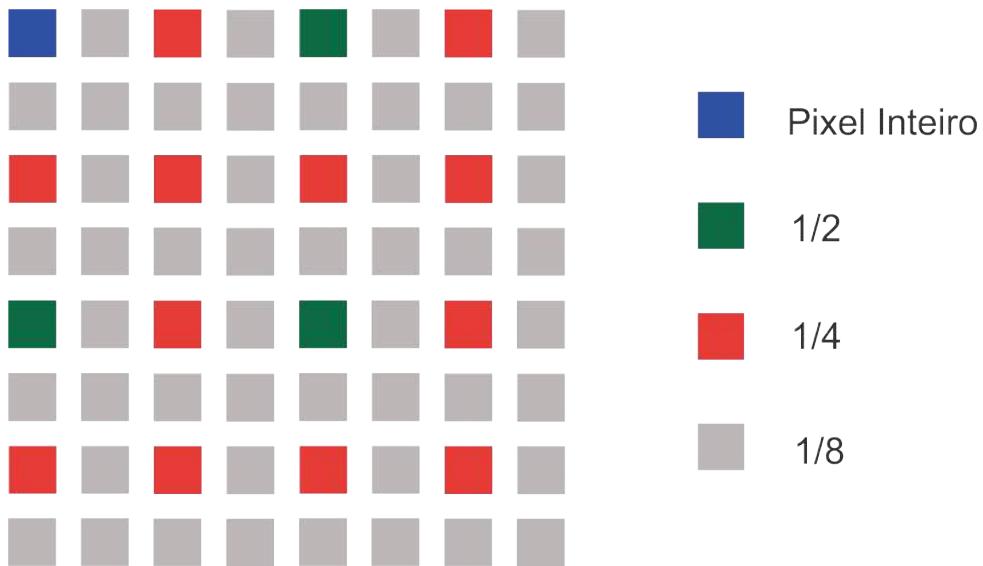

executada, no intuito de refinar o resultado do bloco inteiro com a busca de movimentos mais suaves. Portanto, a FME é um processo que gera subamostras fracionárias em torno das amostras inteiras, de modo que, essas amostras fracionárias são obtidas através de interpolação com filtros de resposta ao impulso finito, *Finite Impulse Response* (FIR), e *Bilineares*.

O codificador AV1 estabelece um conjunto de 48 filtros para uso, sendo eles 42 filtros do tipo FIR ou Bilinear, que variam de 8 a 2 taps, com uma precisão de 1/8 de amostra para luminância, e seis filtros de identidade (RIVAZ; HAUGHTON, 2019). Os filtros de interpolação definidos no AV1 são:

- i **Regular**: um filtro de interpolação baseado em Lagrange que pode ter 6 ou 4 taps (7 filtros em cada caso);

- ii **Smooth**: um filtro de suavização projetado na janela Hamming que pode ter 6 ou 4 taps (7 filtros em cada caso);

- iii **Sharp**: um filtro de 8 taps baseado na Transformada Discreta dos Cossenos (*Discrete Cosine Transform* - DCT);

- iv **Bilinear**: um filtro de 2 taps usado em operações de interpolação rápida.